Lehrstuhl Prof. Dr.-Ing. Snelting

# **SSA-based Register Allocation for Compressed** Machine Code

Masterarbeit von

## Maximilian Stemmer-Grabow

an der Fakultät für Informatik

**Erstgutachter: Zweitgutachter:** Betreuender Mitarbeiter: M. Sc. Andreas Fried

Prof. Dr.-Ing. Gregor Snelting Prof. Dr. rer. nat. Bernhard Beckert

Abgabedatum:

20. Dezember 2021

## Abstract

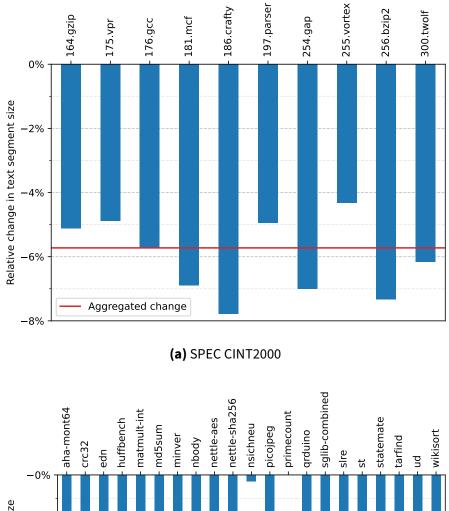

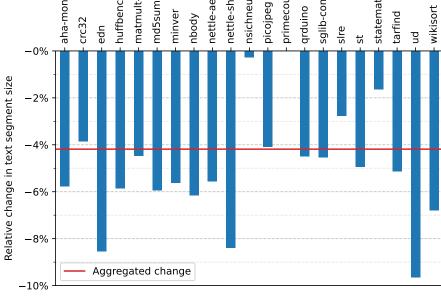

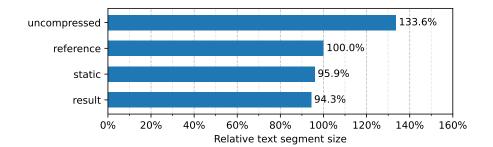

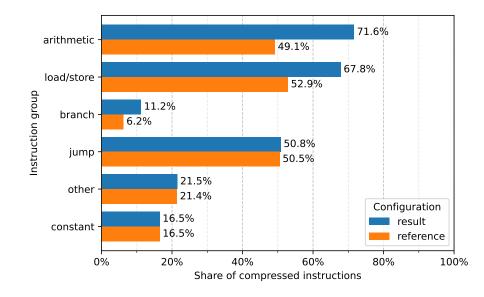

Many RISC instruction sets include compressed instruction variants to improve code density. Due to limited encoding space, these compressed variants are restricted, often in terms of the registers they can be used with. This means that explicitly modeling these restrictions during register allocation can be leveraged to improve compression of the resulting code. In this thesis, we present an extension to the SSA-based register allocator used in the LibFirm framework that enables compression-aware register allocation. It is an opt-in optimization that can be enabled for backends by specifying compression requirements for instructions. It supports specifying a limited subset of *compressible* registers to be used in compressed instructions, 2-address requirements for instructions, and combinations of these requirements. We implement the optimization for LibFirm's RISC-V backend and evaluate the resulting code size improvements: Using the optimization, we can observe an overall aggregated reduction of text segment sizes in compiled object files of around 4.2% or 5.7% in Embench or SPEC CINT2000 benchmark suites, respectively. At the same time, the overall number of generated instructions does not increase by more than 0.2% for any of the benchmarks from SPEC CINT2000. This indicates that the optimization does not otherwise negatively affect the performance of the generated code.

## Zusammenfassung

Viele RISC-Architekturen enthalten zur Verringerung der Codegröße komprimierte Instruktionsvarianten. Diese sind in ihrer Funktionalität beschränkt, was häufig die Auswahl von Registern für Operanden und Ergebnisse betrifft. Deswegen kann die Codegröße dieser Architekturen verringert werden, indem diese Beschränkungen auch im Compiler beachtet werden. Diese Arbeit enthält eine Erweiterung des auf SSA aufbauenden Registerallokators des LibFirm-Frameworks, die Code-Kompression bei der Registerallokation explizit modelliert. Die Optimierung kann für Backends in LibFirm genutzt werden, indem für alle Instruktionen die Bedingungen spezifiziert werden, unter denen sie komprimierbar sind. Dazu können für komprimierte Instruktionen Beschränkungen auf eine Teilmenge von komprimierbaren Registern und 2-Adress-Bedingungen angegeben werden, sowie Kombinationen davon. Die Optimierung wurde für das RISC-V-Backend in LibFirm implementiert und die Verbesserung der Codegröße untersucht: Mit der Optimierung lässt sich die Größe von Textsegmenten in Objektdateien im Mittel um etwa 4,2% (für Embench) bzw. 5,7% (für SPEC CINT2000) verringern. Gleichzeitig steigt die Gesamtzahl von generierten Instruktionen bei keinem der SPEC-Benchmarks um mehr als 0.2% an, die Optimierung verschlechtert also nicht die Performance des generierten Codes.

# Contents

| 1 | Introduction                                                                                                                                                                                                                                                                                                            | 7                                                   |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| 2 | 2.1       Compressed ISAs       1         2.2       RISC-V Compressed Instruction Set Extension       1         2.3       LibFirm Architecture       1         2.4       Register Allocation in LibFirm       1         2.4.1       Copy Optimization Heuristic       2                                                 | 11<br>14<br>17<br>20<br>21<br>25                    |

| 3 | <ul> <li>3.1 Irregular Architectures and Register Allocation</li></ul>                                                                                                                                                                                                                                                  | 27<br>27<br>28<br>30                                |

| 4 | 4.1       Design Requirements       3         4.2       Compressibility Specification       3         4.3       Compression Requirement Handling       3         4.3.1       Static Register Order       3         4.3.2       Affinity Graph Structure       4         4.3.3       Copy Optimization Heuristic       4 | <b>33</b><br>33<br>35<br>37<br>37<br>40<br>42<br>46 |

| 5 | 5.1       Scope and Affected Metrics       4         5.2       Benchmarking Data Set       5         5.3       Setup       5                                                                                                                                                                                            | <b>49</b><br>50<br>51<br>56                         |

| 6 | Conclusion and Future Work                                                                                                                                                                                                                                                                                              | 53                                                  |

| A | Appendix 7                                                                                                                                                                                                                                                                                                              | 71                                                  |

# **1** Introduction

Apart from their semantic correctness, programs generated by optimizing compilers can be evaluated according to different metrics: These include performance when running the code or the overall size of the resulting executables. Optimizing for small code size is especially important when space is limited, for example when dealing with embedded applications, but can also in turn affect code performance. The associated metric is called *code density*, which describes the required code size of a program which performs a specific function – a higher code density implying a smaller footprint for the executable.

Architectures based on the RISC philosophy (short for *reduced instruction set computer*) are successful due to being easier to specify and implement in hardware, but their trade-offs often negatively affect code density of generated code. This difference in code size between traditional fixed-length RISC and CISC code has previously been surveyed and placed at around 25% on average [1]. Uniform instruction lengths common in RISC instruction sets simplify the architecture, but also reduce flexibility when it comes to the amount of information encoded in specific instructions. RISC architectures are also often designed as load-store architectures, separating instructions accessing memory from those operating on data in registers. This lowers the required number and complexity of different instruction types, but may also increase the number of instructions in a given program when compared to typical CISC architectures.

To counteract problems with lower code density, several architectures have introduced the notion of *compressed instructions*, instruction variants that have shorter encodings than the standard instruction length. Due to the limited encoding space available for these shortened instructions, they can only cover a part of the original instruction set: Not all instructions can be included and there need to be restrictions on the information that is encoded in the instructions themselves. Often, this is achieved by requiring operands or results to be in a certain subset of all available registers, or an operand and the result being placed in the same register (i.e., conforming to a 2-address instruction format).

The RISC-V architecture this thesis is focused on includes compressed instructions in its C extension (also abbreviated RVC). They are also restricted in this way: For example, RISC-V defines a sub instruction which subtracts the contents of two registers: sub rd, rs1, rs2 places rs1 - rs2 into the register rd. In the base instruction set, either operand can be chosen from any of the 32 general purpose registers available in RISC-V, and the result can be placed in any register. The compressed sub instruction variant requires the result to overwrite the first operand (rs1 and rd have to be identical). Additionally, all involved registers have to be in the subset of eight *compressible* registers instead of the full register set. Both of these requirements need to hold in order to be able to choose the compressed instruction variant. A more detailed description of the RISC-V Compressed extension will be presented later in section 2.2.

For cases such as RVC where the requirements for compressed instructions are related to the register set, this introduces a dependency on the result of *register allocation* in the compiler: Whether an instruction can be expressed in a compressed format depends on which values in the program are placed in which physical register.

In general, operand placement in registers is often somewhat restricted, especially in CISC architectures. For example, architectures may require that operands are placed in certain registers in order for them to be used with a specific instruction. Of course, these restrictions are *mandatory*: They have to be fulfilled in order to generate correct code for the architecture. For this reason, this kind of restriction is already modeled in compilers and compilers are aware of it during register allocation.

Restrictions related to compression we are concerned with in this thesis are different, however: Compression-related requirements are optional and not required to generate correct code. In cases where the compression restrictions cannot be fulfilled, the uncompressed instruction encoding can be chosen instead, the penalty being the larger code size that comes with using the uncompressed instruction. This makes trying to fulfill compression-related restrictions a trade-off: As many of them as possible should be fulfilled, but without introducing more instructions overall.

However, modern compilers usually do not directly model and optimize for compression requirements when performing register allocation. This thesis aims to improve code density by explicitly making the compiler aware of these requirements. To do this, we focus on the compressed instruction extension for RISC-V and modify the register allocation step which is part of LibFirm, a graph-based intermediate representation library. It includes backends for multiple instruction sets, RISC-V being one of them.

LibFirm's register allocation includes a step called *copy elimination* (or *copy optimization*). It employs a heuristic to try to find a valid register allocation that also minimizes the number of times values need to be copied (or moved) between different registers when running the program. To simultaneously maximize the number of instructions that are compressed in the final compiled program, we extend this step to account for the compression requirements of specific instructions. This also requires a way to express which instructions can be compressed (and under which conditions) in the architecture-specific backends for LibFirm. In the case of the **sub** operation, the backend can provide the information that there is a corresponding compressed instruction which requires the first operand to be in the same register as the result as well as all involved registers to be in the compressible register subset. The copy elimination algorithm can incorporate this into the placement of the operands and result of the instruction. This can then be applied for every instruction that may be compressed if similar requirements hold. The most important design goals for this extension include:

- The quality of the register allocation should not be negatively affected. Register allocation has a large impact on the performance of the generated code: Its result determines the number of times data has to be copied between registers or registers and memory when running the code. This not only affects runtime performance, but also the resulting code size (via the number of move instructions between registers remaining in the program code).

- The extension should also keep the additional complexity introduced into the register allocation algorithm itself to a minimum: Improved compression is desirable, but should not come at the cost of considerably longer running time of the register allocator. It also should not include changes to the allocator that make it much harder to understand and reason about.

We evaluate the results of the optimization by comparing resulting code sizes in benchmarks using cparser, a C compiler which uses LibFirm for intermediate code representation, optimization, and code generation.

The thesis is structured in the following way: Chapter 2 contains an introduction to the context of and the concepts required in the thesis. This includes compressed instruction sets as well the LibFirm infrastructure and its theoretical foundations. Chapter 3 provides an overview over other works relevant in this context: Works dealing with register allocation confined by restrictions present in many computing architectures. It also surveys other works that deal with compiling code for architectures that support compressed machine code. Contributions of the thesis are structured in this order: An overview over the design of the compression optimization as well as how it is implemented can be found in chapter 4. Measurements, comparisons, and results are presented in chapter 5. Chapter 6 outlines starting points for possible future work in the context examined here and concludes the thesis.

# 2 Foundations

This chapter serves as an introduction to the basic concepts and ideas that are relevant to this thesis. We will first take a look at the rationale and design of compressed instruction sets as well as some specific examples in section 2.1, followed by a more in-depth look at the compressed instruction extension for RISC-V in section 2.2. A brief introduction to the LibFirm approach and its architecture is contained in section 2.3, especially concerning where and how register allocation is integrated there. LibFirm's register allocation approach and especially its copy optimization step is covered in section 2.4.

### 2.1 Compressed ISAs

As mentioned in the previous chapter, the concept of compressed instructions is related to optimizing *code density*. A higher code density corresponds to a smaller total size of the instructions required for a particular program when compiled for a specific architecture. Especially for RISC architectures with uniform instruction lengths, this is a challenge: Different types of instructions typically also have different requirements for the amount of data that is useful to include in them, e.g. depending on the number of operands or the desirable length of immediate values. Many RISC architectures are also designed as load-store architectures: These isolate instructions for transfer of values between memory and registers from instructions operating on them. As an example, this means that as arithmetic instructions only operate on values in registers, the additional required load and store instructions often lead to overall higher instruction counts. In contrast, CISC architectures are often designed with variable-length instruction encodings.

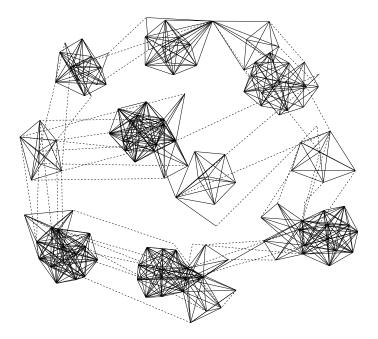

For example, let us examine the code generated for a simple function that computes the maximum of two operands with one of them being scaled beforehand:

```

int max42(int a, int b) { return (a * 42 > b) ? a : b; }

```

Figure 2.1 shows code generated for RISC-V (with 32-bit instruction length and without compressed instructions) and x86. In this case, even though both code versions contain five instructions, there is a difference in code size: Due to the variable-length encoding of x86 instructions, they only require 11 bytes while the RISC-V instructions take up 20 bytes.

As a matter of course, this difference between code sizes varies a lot across different code samples and architectures. Overall, in a survey of code densities of different

```

max42:

02a00793

li

a5, 42

02f507b3

mul

a5, a0, a5

00f5c463

blt

a1, a5,

<max42+0x10>

00058513

a0, a1

mv

00008067

ret

(a) RISC-V

max42:

89 d0

%edx, %eax

mov

$0x2a, %ecx, %edx

6b d1 2a

imul

39 c2

%eax, %edx

cmp

0f 4f c1

cmovg %ecx, %eax

cЗ

ret

(b) x86

```

Figure 2.1: Comparison between RISC-V and x86 code generated for the function int

max42(int a, int b) { (return a \* 42 > b) ? a : b; }.

instruction sets, Weaver and McKee found code sizes for fixed-length RISC instruction sets to be an average of about 25% larger than those for CISC instruction sets [1].

Compressed instructions aim to reduce this difference by introducing variablelength encodings: There are multiple RISC instruction sets that include the notion of compressed instructions, including RISC-V. These may be included as variants of or as extensions to the original fixed-length instruction sets. In our example above, using the compression extension for RISC-V, two of the five instructions could be replaced by compressed instructions. These only take up 16 bits each and in this case bring down the code size from 20 to 16 bytes. When evaluating instruction sets that support compression or a specific group of instructions, we use the term *compressed instruction rate* to describe the share of instructions that are compressed (in the example above, it is 40%).

Let us review and compare the approaches for enabling compression in some architectures most relevant in the context of this thesis:

**ARM and Thumb** Thumb is an instruction set based on the ARM instruction set [2], which was introduced to achieve higher code density when compared to ARM code by utilizing instructions with a length of 16 instead of 32 bits. Most of these shortened instructions are closely related to ARM instructions, but not all of them are directly expandable into uncompressed instructions. Not all instructions in the ARM instruction set are available as shortened instructions in Thumb, and available instructions are constrained: For example, of the 16 general purpose registers available with ARM, only eight are available as general purpose registers with Thumb. Three

additional registers have special functions with certain instructions, but are not arbitrarily accessible. Processors can support both Thumb and ARM instruction sets simultaneously: In this case, explicit mode switch instructions can be used to change between ARM and Thumb execution modes. Other works have investigated how compression can be optimized for this kind of explicitly mode-switching architecture (more details can be found in section 3.2).

Instructions in the original Thumb specification are not designed to provide the full functionality from the ARM instruction set. To alleviate this, Thumb-2 (2003) [2] extends Thumb with new instructions, especially in 32-bit encodings: These aim to reintroduce most functionality from the ARM instruction set missing from Thumb, but are separate instructions not included in ARM. This effectively converts Thumb into a mixed-length instruction set which aims to cover similar functionality as the separate, fixed-length 32-bit ARM instruction set. This also removes the need for changing execution modes in between instructions by allowing 16- and 32-bit encoded instructions to be directly intermixed. To be able to target both Thumb and ARM, the Thumb-2 extension also includes an assembly syntax that can be compiled to both variants, called *Unified Assembly Language* (UAL for short). Note that the Thumb-2 extension replaced the original instruction set and is now only referred to as Thumb in its specification.

**MIPS** MIPS16e and its successor MIPS16e2 are extensions to the MIPS32 and MIPS64 instruction sets [3] which include 16-bit instructions. Processors implementing them have an execution mode that has to be explicitly set: A mode switch instruction needs to be executed before any of these additional 16-bit instructions. For most instructions in the 16-bit execution mode, only a subset of eight registers is available instead of the full 32 registers available with 32-bit instructions. Only compressed move instructions support access to all registers.

There is also a more recent addition which removes the need for explicit execution mode switching: microMIPS [4] is an extended ISA variant based on MIPS32/64 which includes additional instructions with 16-bit length, similar to those defined in MIPS16e(2). microMIPS is a superset of MIPS32/64 and hence also allows the longer, uncompressed instructions to be used. As it does not require an explicit mode switch, instructions can be freely intermixed between microMIPS' additional 16-bit and regular 32-bit MIPS instructions. Similarly to MIPS16e(2), most instructions are restricted to access a subset of eight registers (registers 2-7, 16, and 17 in MIPS register encoding) [4].

As microMIPS has been introduced to replace MIPS16e(2), it is now the preferred way of implementing compressed instructions for MIPS. MIPS16e has been removed from the MIPS specification in its Release 6 [4, p. 13].

**RISC-V** RISC-V [5] is designed as a modular instruction set specification: Its full functionality is split across multiple extensions that add instructions to the base instruction set. Compressed instructions are contained in extension C, short for

| Format                 | Meaning              | 15     | 14   | 13   | 12    | 11              | 10  | 9   | 8     | 7      | 6   | <b>5</b> | 4   | 3    | <b>2</b> | 1 | 0 |

|------------------------|----------------------|--------|------|------|-------|-----------------|-----|-----|-------|--------|-----|----------|-----|------|----------|---|---|

| $\mathbf{CR}$          | Register             |        | fu   | nct4 |       |                 | rd  | /rs | 1     |        |     | 1        | :s2 |      |          | 0 | p |

| CI                     | Immediate            | f      | unct | 3    | imm   |                 | rd  | /rs | 1     |        |     | ir       | nm  |      |          | 0 | p |

| $\mathbf{CSS}$         | Stack-relative Store | f      | unct | 3    |       |                 | imm |     |       |        |     | 1        | s2  |      |          | 0 | p |

| CIW                    | Wide Immediate       | f      | unct | 3    |       |                 |     | imr | n     |        |     |          |     | rd′  |          | 0 | p |

| $\operatorname{CL}$    | Load                 | f      | unct | 3    | ir    | nm              |     |     | rs1   | /      | in  | nm       |     | rd'  |          | 0 | p |

| $\mathbf{CS}$          | Store                | f      | unct | 3    | ir    | nm              |     |     | rs1   | /      | in  | nm       | ]   | rs2' | ,<br>    | 0 | p |

| $\mathbf{C}\mathbf{A}$ | Arithmetic           | fu     |      |      | unct6 |                 |     | rd  | .'/rs | 1'     | fur | nct2     | ]   | rs2' |          | 0 | p |

| CB                     | Branch/Arithmetic    | funct3 |      |      | of    | offset rd'/rs1' |     |     | 1'    | offset |     |          |     | 0    | p        |   |   |

| CJ                     | Jump                 | funct3 |      |      |       | jump target     |     |     |       |        |     |          | 0   | p    |          |   |   |

Table 2.1: RISC-V C instruction formats, taken from the RISC-V specification [5].

*Compressed.* The extension was suggested by Waterman in 2011, explicitly to improve energy efficiency for execution when compared to the fixed-length RISC-V instruction set [6]. It defines compressed instructions which are freely intermixable with uncompressed instructions from the base instruction set or other extensions. We will now take a more in-depth look at the design of the extension in the following section.

### 2.2 RISC-V Compressed Instruction Set Extension

The RISC-V specification [5] defines three base instruction sets with different register widths: 32-bit (RV32), 64-bit (RV64), and 128-bit (RV128). The C extension (also called RVC) can be combined with any of these instruction sets. The extension defines instructions with a length of 16 bits that can all be expanded into corresponding uncompressed instructions which are semantically equivalent. Instructions with compressed variants are contained in the base instruction set or in the F and D extensions (which provide hardware floating-point handling). The standard provides nine different instruction layout types in this 16-bit format, shown in table 2.1. The encodings are chosen from these formats according to the required fields in each specific compressed instruction. During execution, compressed instructions can be expanded into their long-format equivalent by the processor in the decoding step. The opcode encoding space for compressed instructions is reserved and not used in uncompressed base instructions sets or other extensions. On machines which support the extension, RVC allows compressed and uncompressed instructions to be freely intermixed without the use of a flag or special instruction to togele instruction modes. RVC also relaxes the alignment requirements for uncompressed instructions, which precludes the need for padding when switching between compressed and uncompressed instructions (as such padding would negatively affect code size).

The fact that compressed instructions correspond directly to uncompressed instructions and can be intermixed as described make RVC a good candidate for a prototype implementation of explicitly incorporating compression into register allocation. This is why we chose it as the focus for this thesis. RISC-V provides the following workflow for creating code that includes compressed instructions: Explicit mnemonics for compressed instructions with the prefix c do exist as part of RISC-V assembly. However, these are not required to generate compressed code when using the assembler that is part of the RISC-V toolchain. As any compressed instruction has an uncompressed counterpart, the assembler can select compressed variants for those instructions which comply with all compression requirements, even if they are not explicitly indicated as compressible in the assembly code.

This allows a form of *implicit* compiler support: The compiler does not need to be aware of compressed instructions or their requirements if it emits assembly code that is passed to the RISC-V assembler. Instructions which satisfy all requirements are then transformed into their compressed versions. LibFirm uses this fact in its RISC-V backend and emits the same assembly code for platforms with or without support for the C extension, passing the selection of compressed instructions on to the assembler. However, as compared to this "incidental" compression, explicit compiler support can increase the number of overall instructions that satisfy the requirements for compressed instructions, hence reducing code size further.

We will now take a closer look at the specific compression requirements included in RVC. Evaluating whether a single instruction can be compressed means evaluating each compression requirements associated with it. Not all types of instructions have compressed encodings, so the very first criterion is the instruction having an opcode that also has a compressed variant. We will outline below which other types of requirements RVC imposes on compressed instructions apart from this.

**Immediate and Offset range** Many values that are directly encoded in compressed instructions are limited to a shorter length than in their uncompressed counterparts: This applies to immediate values for register-immediate or constant generation instructions. These have a (signed) immediate field which is limited to 6 bits. Branch and jump target offsets are also limited to 8 and 11 bits, respectively.

**Compressible registers** Regular RISC-V instructions that can operate on any register include 5-bit register specifiers to select it (making all 32 registers of the RISC-V register set accessible unless specifically forbidden by the specification). Many compressed instructions can only accomodate 3-bit *shortened register specifiers*, which can select from only eight of the available registers. As shown in table 2.1, this is the case for the CIW, CL, CS, CA, and CB instruction formats. The registers which can be specified this way are registers x8 to x15 (called s0-s1 and a0-a5 in the RISC-V ABI). These registers are most commonly used as they are the ones defined in the RISC-V calling convention to be used to pass the first parameters for function calls, which are passed in registers instead of on the stack. Registers in this subset are referred to as *compressible registers* in this thesis. When combined with the hardware floating-point extensions, there is a similar subset that covers eight

of the 32 floating-point registers which can be addressed using shortened register specifiers.

**2-Address Format** Instructions with input and output registers may also have a requirement for a 2-address instruction format. This applies for CR, CI, CA, and CB instruction formats. RISC-V specifies uncompressed instructions in 3-address formats where applicable, meaning that operands can be specified separately from the destination. With a 2-address requirement, one operand must be in the same register as the result. This means the first operand cannot be used again in later instructions without moving it to another register prior to executing the 2-address instruction.

Note that for instructions with multiple requirements, every single one of them has to be fulfilled in order for the instruction to be compressible. For example, the **sub** instruction we used as an example in a previous chapter uses the CA format: It combines a 2-address requirement with the need for operands to be in compressible registers. If either of these requirements is not fulfilled, the uncompressed instruction has to be chosen (which has neither of these restrictions). This means that all compression requirements for an instruction are linked: Only fulfilling them partially while others remain unmet does not offer any advantage with respect to compression. However, fulfilling requirements partially may of course affect compressibility of other instructions.

The RISC-V specification [5] defines compressed variants for a number of instruction types, each with a combination of the different limitations described above. The following instructions are compressible:

- Load and store instructions with a source or target register that is compressible. However, stack-pointer-relative compressed loads and stores can be used with all registers. The offset of the specified address from a register is limited to 5 bits (or 6 bits for stack-pointer-relative loads and stores) and is scaled to increase the range.

- **Jump** instructions with a limited offset. This includes jumps to addresses in registers and jump and link instructions. Compressed **branch** instructions exist for comparisons of a compressible register with zero.

- **Constant generation** instructions with small immediates that fit into 6 bits.

- Move instructions from and to all registers.

- Register-based **arithmetic** instructions (and, or, xor, and sub instructions) with 2-address format and with all operands and the result being in compressible registers.

- Register-immediate **shift** instructions with 2-address format and partially with compressed register requirements.

• Register-immediate and register-register **add** instructions with 2-address format. Note that for add instructions, operands are not restricted to the compressible register subset. The compression requirements for add instructions are relaxed when compared to other arithmetic instructions because they are usually the most frequently used arithmetic instructions.

The extension also includes special instructions for operations related to the stack pointer: Addition of scaled immediates onto the stack pointer can be used to adjust the stack pointer, and stack-pointer-relative adds that write to a compressible register are useful to generate pointers to values on the stack.

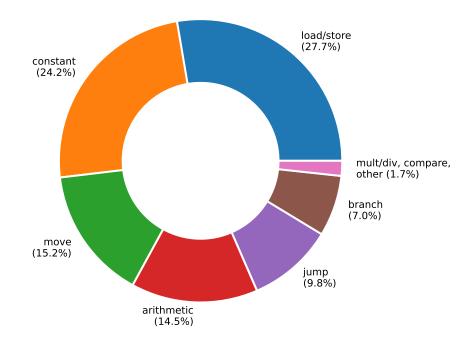

From this overview, it is already apparent that an improved compression rate cannot be expected for all of these groups when adjusting only the register allocation step in the compiler: All move instructions are already compressible regardless of the result of register allocation, but their overall number is of course affected by the quality of the register allocation result. Whether jumps and constant generation instructions are compressible depends on the offset and immediate sizes. This is not directly related to register allocation. Only a specific subset of all available branch instructions is potentially compressible. Most relevant when optimizing the register allocation step are therefore load/store and arithmetic instructions, as their compressibility requirements are directly related to the register allocation. More details on the relative frequency of the different instruction groups in benchmark code and the share of compressed instructions in them can be found in chapter 5.

### 2.3 LibFirm Architecture

To understand register allocation in the context of LibFirm, let us first introduce the way it represents programs: LibFirm uses a graph-based intermediate code representation (IR) called Firm [7]. Backend infrastructure to transform this representation into executable code for several architectures is included in LibFirm, as well as a selection of code analyses and optimizations.

LibFirm's intermediate representation is in SSA form (short for *single static assignment*). SSA requires variables in the IR to be assigned only once and then only used afterwards. Reassigning different values to a single variable is disallowed, as is usage of values without a prior definition. These restrictions have many advantages for algorithms and optimizations used in the compiler.

In SSA, dependencies of values on control flow are modeled by using so-called Phi  $(\phi)$  functions: Phi functions choose from a list of previously defined variables based on where control flow originated from and define a new variable with the respective value. Actual hardware architectures in use do not directly support executing Phi functions, so they need to be resolved during compilation: This is done by replacing them with moves between registers (and/or memory) at appropriate places in the program.

Firm being a graph-based representation means that programs are represented as a collection of graphs: A function corresponds to a directed graph. Data and control flow are represented by nodes of different types and edges between these nodes. SSA values such as the results of data flow operations correspond to nodes. Control flow is also encoded in the graph: Instructions related to control flow and basic blocks are also represented as nodes. Their relationships (such as the nodes included in a given basic block or the operands of arithmetic instructions) correspond to directed edges between them.

An example for a Firm graph is shown in figure 2.2. It depicts the max42 function we introduced as an example in section 2.1. Each node is shown with the type of operation it represents (such as Mul for multiplication), the type of the value (also called *mode*, the Mul node representing a signed integer or Is), and a unique identifier. Basic blocks are depicted as boxes around the nodes they contain. Proj nodes are used to extract values for cases where nodes output tuples of multiple values. We can also see a Phi node representing the Phi function which selects the correct value for the ternary operator in the function.

Using this representation, LibFirm can perform a multitude of optimizations expected from an optimizing compiler directly on the graphs: This involves transformations of the input graph that do not alter the semantics of the input program, but e.g. improve the performance of the resulting code.

In the backend, the optimized graphs can be converted into code for the target architecture. Even in the backend, the graphs remain in SSA form, but are modified and annotated with additional information. Highly simplified, this includes the following steps:

- During instruction selection, nodes are replaced with architecture specific operations (often representing available instructions on the target architecture).

- Scheduling means arranging the nodes in a way that conforms to the dependencies between values in the program and that can be used as the order instructions are emitted in.

- The register allocator assigns values to physical registers. Before this step, most generic nodes in the graph have already been replaced with architecture specific ones. When determining a register assignment, the register allocator also needs to make sure that enough registers are available to find a valid allocation: To guarantee this, some values may need to be transferred to memory first (which is called *spilling*). The register allocator needs to ensure that after being run, each value (each node in the Firm graph) is assigned a valid register, without conflicts between values that may be used at the same time in the program. Register assignments are annotated as attributes of the Firm nodes. As this is the main phase we are concerned with in this thesis, we will discuss register allocation in LibFirm in more detail in section 2.4 below.

- After handling requirements concerning how functions are called and how the stack is organized, the target architecture code can be generated and emitted.

To be able to use this infrastructure to compile code in a high-level programming language, we use cparser, a C compiler built around LibFirm: It is a LibFirm frontend for C, performing the transformation into LibFirm's intermediate representation.

### 2.4 Register Allocation in LibFirm

LibFirm performs register allocation based on the formalization as a graph-coloring problem. A vertex coloring of an undirected graph is an assignment of colors to each node in the graph such that no two nodes that share an edge also share the same color. Register allocation can be expressed as such a problem using the *interference graph*. This is an undirected graph representing the relationship between the variables in the program. Variables or values are nodes in the interference graph, and edges are placed between two nodes if they are *live* at the same time in the execution of the program. Variables are considered live if their value could be needed later in the runtime of the program. This means that variables that are live at the same time cannot be assigned the same register: They are considered *interfering*.

When interpreting register allocation as a coloring problem, available registers correspond to the colors that can be used to color the graph. A valid register allocation then corresponds to a valid coloring for the nodes of the interference graph. This ensures that no two nodes sharing an edge are colored in the same color (i.e., no interfering variables are assigned the same register).

Register allocation is also related to *spilling*: Spilling refers to deciding whether and which values to transfer from registers into memory. This is required in order to produce a valid register allocation in cases where more than the available number of registers would be required without evicting some of them to memory.

This approach to register allocation as a graph-coloring problem was introduced by Chaitin in 1982 [8]. On arbitrary interference graphs, finding a valid coloring or even finding the number of required colors for a coloring (the *chromatic number*) is NP-complete. For this reason, Chaitin's algorithm uses the node degrees in the interference graph as a heuristic for coloring and spilling decisions. Chaitin's work has been extended or built upon in numerous ways [9] [10] [11], probably most notably by Briggs in 1992 [12]. In these algorithms, spilling and coloring are interlocked: During coloring, it may be required to iteratively spill more values in order to find a valid register allocation.

As we discussed above, SSA form is used throughout LibFirm's backend without deconstructing it for further handling. Instead, the transformations performed on the graph by the backend yield a structure that is more and more restricted and contains additional annotations. For example, scheduling or register assignment information is added.

This also means that when register allocation is performed, the program's intermediate representation is still in SSA form. For register allocation, this presents advantages related to the fact that SSA programs' interference graphs are *chordal*. Chordal graphs are triangulated, meaning that for all cycles of more than three nodes, there are edges not part of the cycle that connect two nodes in the cycle.

The theoretical foundations of the current LibFirm approach to register allocation based on the special characteristics of SSA interference graphs were suggested in works by Hack and Goos. They showed that for a hypothetical fully uniform register set, register allocations for programs can be found in polynomial time [13]. More practically relevant, Hack introduced the current principles of register allocation in LibFirm in his PhD thesis from 2006 (published in 2007) [14]: This includes register allocation on chordal graphs, which allows to decouple spilling from register allocation. After spilling, register allocation on chordal graphs can be performed without possibly having to iteratively spill more values (like it is required when performing register allocation based on the Chaitin/Briggs algorithms).

#### 2.4.1 Copy Optimization Heuristic

Hack also suggested the predecessor of the current *copy coalescing heuristic* used in LibFirm. Copy coalescing, copy elimination, or *copy optimization* attempts to reduce the number of move instructions that are required in the program. This is achieved by intelligently selecting a register allocation which places values which would need to be copied between registers into the same physical register. This heuristic is the component of LibFirm's register allocator which has the largest impact on the quality of the resulting register allocation.

Before running the heuristic, an initial assignment of registers is determined, and the heuristic tries to optimize it without invalidating the coloring. Note that in the descriptions below, assignment of a value to a specific register is referred to as *coloring* its node with the color corresponding to the register.

To aid the explanations below, we use pseudocode formulations of parts of the heuristic. These are shown in algorithms 1, 2, and 3. All of these listings are adapted from section 4.5.2 of Hack's dissertation [14], with changes as they are reflected in the current implementation of the heuristic used in LibFirm.

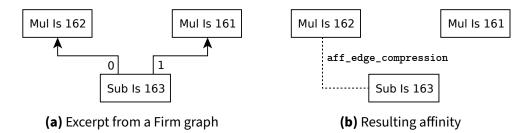

**Affinities and Affinity Graphs** The heuristic is based on the concept of the *affinity* graph of the program. This is an extension to the idea of the interference graph. It is an undirected graph that also contains values as nodes, but places edges between nodes that are *copy-related*: This means that finding a register allocation which assigns them the same color (places them in the same physical register) saves a move instruction between the two.

The purpose of the copy optimization heuristic is finding a valid register allocation that satisfies the maximum number of affinities. More precisely, it aims to fulfill the set of affinities which would impose the highest runtime cost if their associated move instructions could not be elided. To be able to model this, affinity edges are also assigned a *weight* representing the cost of not fulfilling the affinity. The cost function is adjustable in LibFirm: The default cost function is based on a simple heuristic estimating instruction execution frequency. **Affinity Chunks** The reflexive-transitive closure of the affinity relation yields *affinity components*. These components of the affinity graph which are connected by edges are not always free of internal interferences. If they do have internal interferences, the nodes in the component cannot all be colored with the same color, and not all affinities they include can be fulfilled.

To be able to handle this situation, nodes are put into *affinity chunks*, interferencefree subsets of affinity components. Thus they can in principle all be colored with the same color. In practice, this is not always possible. In that case, affinity chunks can be split further.

| Alg  | Algorithm 1 Affinity Chunk Construction                                                          |  |  |  |  |  |

|------|--------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 1: j | 1: <b>procedure</b> BUILDAFFINITYCHUNKS(IG G: (nodes V, interference edges E, affinity edges A)) |  |  |  |  |  |

| 2:   | for $v \in V$ do                                                                                 |  |  |  |  |  |

| 3:   | $v.chunk \leftarrow New chunk$                                                                   |  |  |  |  |  |

| 4:   | 4: for $xy \in A$ sorted by edge weight from high to low do                                      |  |  |  |  |  |

| 5:   | $\triangleright$ Add all nodes in y's chunk to x's chunk                                         |  |  |  |  |  |

|      | if there are no interferences between the two chunks                                             |  |  |  |  |  |

| 6:   | ABSORBCHUNK(x.chunk, y.chunk)                                                                    |  |  |  |  |  |

The initial affinity chunks are constructed greedily. Pseudocode for the construction procedure is shown in algorithm 1. Starting out with a single node, affinity chunks are grown by collecting other nodes connected with affinities, going in the order of decreasing affinity edge weights. At each step, this only needs to ensure that newly inserted nodes do not interfere with any of the nodes already in the chunk.

**Chunk Weights** When executing the heuristic, the weights of all affinity edges contained in a chunk are aggregated for all its nodes. This avoids having to handle each node in the chunk separately. Lists of nodes from other chunks interfering with any node in the chunk are also maintained per chunk for performance reasons. The summed weight of all affinity edges which connect nodes contained in the chunk is referred to as *chunk weight*.

Every chunk has an associated metric which indicates its favorability for each color. It is based on the number of nodes in the chunk that are colorable in the respective color; nodes that are very constrained in their color choice are weighted higher. From this, an order of the colors can be derived, which is called the *color preference* of the chunk.

**Chunk Recoloring** The chunk recoloring algorithm is a recursive method for heuristically finding the best color for a chunk. A simplified overview of the variant currently used in LibFirm is shown in algorithm 2.

Colors for the chunk are tried in the order that corresponds to the color preference value. When the color col is tried, recoloring follows this pattern: Generally, the target is to color all nodes in the given chunk with col. If col is allowed for a node n,

## Algorithm 2 Chunk Recoloring

| 1:  | <b>procedure</b> ColorAffinityChunk(IG $G$ , Chunk $C$ , Queue $Q$ )                                            |

|-----|-----------------------------------------------------------------------------------------------------------------|

| 2:  | $\triangleright R$ is the set of registers in a register class (the set of colors available to color the graph) |

| 3:  | Compute color preference, order colors in $R$ by preference                                                     |

| 4:  | for $col \in R$ ordered by color preference <b>do</b>                                                           |

| 5:  | Unfix colors for all nodes in $C$                                                                               |

| 6:  | $\mathbf{for}\;n\in C\;\mathbf{do}$                                                                             |

| 7:  | $\triangleright$ Try to recolor n with col and choose a color that is not col for interfering neighbors         |

| 8:  | $\operatorname{ChangeNodeColor}(n, \operatorname{\mathit{col}})$                                                |

| 9:  | $n.fixed \leftarrow 	ext{true}$                                                                                 |

| 10: | $local\_best \leftarrow Best subset of C colored to col$                                                        |

| 11: | ${f if}\ local\_best.weight > best\_chunk.weight\ {f then}$                                                     |

| 12: | $best\_chunk \leftarrow local\_best$                                                                            |

| 13: | $\_$ best_color $\leftarrow$ col                                                                                |

| 14: | if All nodes were colored in <i>col</i> then                                                                    |

| 15: | $\triangleright$ Stop searching if all nodes were recolored                                                     |

| 16: | break                                                                                                           |

| 17: | for $n \in C$ do                                                                                                |

| 18: | $CHANGENODECOLOR(n, best\_color)$                                                                               |

| 19: | $n.fixed \leftarrow 	ext{true}$                                                                                 |

| 20: | $rest \leftarrow C \setminus best\_chunk$                                                                       |

| 21: | $\mathbf{if} \ rest \neq \emptyset \ \mathbf{then}$                                                             |

| 22: | $rest\_chunk \leftarrow New chunk$                                                                              |

| 23: | $\mathbf{for} \ v \in rest \ \mathbf{do}$                                                                       |

| 24: | $v.chunk \leftarrow rest\_chunk$                                                                                |

| 25: | Add $rest\_chunk$ to $Q$                                                                                        |

the recoloring decision is then propagated recursively: Interference neighbors of n with the same color *col* are recolored in another color (any allowed color excluding *col*) and so on. This is performed by the CHANGENODECOLOR procedure on line 8. In case this recursive coloring attempt for the node n is not successful, the process has to be rolled back to the original colors. For this, a list is kept which holds the nodes that were recolored in the current pass as well as their original colors. During this process, the algorithm tracks the "best subset" of the chunk: This is the subset with the largest weight that could be successfully colored in the same color *best\_color* (see lines 11 to 13).

It can occur that not all nodes in the chunk could be successfully colored with the same color. If this is the case, the chunk is then *split* into the part that was brought to the color and a new chunk with the remaining nodes for which this failed (shown in lines 20 to 25).

To ensure termination of the heuristic, recoloring is not continued under the following conditions: In the chunk that is currently recolored, a node's color is fixed when it is successfully recolored. Fixed colors are not to be changed again in the same recoloring step. This prevents nodes from being visited multiple times. Additionally, the recursive recoloring of neighbors is aborted if a fixed limit of recursive steps is reached.

The overall steps necessary to execute the heuristic using these components is shown in algorithm 3: This consists of building the affinity chunks as described above, then creating a priority queue that contains the chunks that are yet to be handled, recoloring them one after another, and then applying the resulting coloring.

|  | Algorithm 3 | Copy | Coalescing | Heuristic |

|--|-------------|------|------------|-----------|

|--|-------------|------|------------|-----------|

| 1: 1 | <b>procedure</b> SolveHeuristic(IG G: (nodes V, interference edges E, affinity edges A)) |

|------|------------------------------------------------------------------------------------------|

| 2:   | Setup data structures                                                                    |

| 3:   | $C \leftarrow \text{BuildAffinityChunks}(G)$                                             |

| 4:   | Initialize empty priority queue $Q$                                                      |

| 5:   | for $c \in C$ do                                                                         |

| 6:   | $\triangleright Q$ keeps chunks sorted by decreasing weight                              |

| 7:   | Insert $c$ into $Q$                                                                      |

| 8:   | $\mathbf{while} \ Q \neq \emptyset \ \mathbf{do}$                                        |

| 9:   | $c \leftarrow \texttt{POP}(Q)$                                                           |

| 10:  | $\triangleright c$ is the chunk from Q with the largest weight                           |

| 11:  | $\operatorname{ColorAffinityChunk}(G,c,Q)$                                               |

| 12:  | $\mathbf{for}v\in V\mathbf{do}$                                                          |

| 13:  | SetRegister(v, resulting color from heuristic)                                           |

### 2.4.2 Mandatory 2-Address Requirements

As indicated in chapter 1, operand placement for some instructions is restricted in many architectures. This means compilers need to be able to model and handle these restrictions in order to generate correct code. For example, certain instructions in the x86 instruction set mandate a 2-address format. We will call these requirements which need to be fulfilled in all cases *mandatory* 2-address requirements. Let us look at how they are implemented in LibFirm:

- Instructions can specify them as a *should-be-same* constraint as part of their definition in the architecture specification. In more complicated cases where it is not yet clear whether such a constraint is required for an instruction, they can also be programmatically added later (during code selection) while building the graphs for the backend.

- While building the affinity graph for the copy optimization heuristic, shouldbe-same constraints are added into the graph as affinity edges. These are placed between the values that must be contained in the same register. The copy optimization heuristic handles these affinities the same way as any other affinities, trying to fulfill as many of them as possible. Note that the heuristic cannot always resolve all of these 2-address requirements.

- After register allocation has taken place, unfulfilled affinities originating from should-be-same constraints may remain. These are handled in a "fixup" step: In case of unfulfilled affinities, this inserts additional copy instructions before and/or after the offending nodes.

# **3 Related Work**

This section provides an overview over other works relevant in the context of this thesis and how their approaches and applicability are different from the work presented here.

## 3.1 Irregular Architectures and Register Allocation

Computer architectures differ in the structure of their register set. The simplest model is to allow all data and operations to be used with all available registers. However, many architectures put restrictions on the use of registers or the combination of operations with values in certain registers. This ranges from few restrictions to highly structured register sets which require that different kinds of data be stored in different registers. The latter is sometimes found especially in embedded architectures.

Architectures with these kinds of restrictions are often called *irregular architectures*. While multiple approaches exist for dealing with these irregularities when performing register allocation, many of them focus more specifically on architectures with highly constrained register architectures. As described in section 2.1 in the previous chapter, there are often restrictions for compressed instructions affecting which registers can be used for specific instructions in order for them to be compressed. These differing requirements for compressed and uncompressed instructions also introduce a slight irregularity into a register architecture (even for those which might otherwise be considered fairly uniform). It is informative to take a look at works concerned with the role of irregularities in register allocation in general in order to identify whether their results are also useful for our goal of improving code compression.

Register allocation based on graph-coloring has been extended to explicitly accomodate architectures with irregularities in a multitude of works. This especially includes handling of multiple related register classes, as this introduces irregularities commonly found in many architectures. Smith and Holloway [15] modified the Chaitin-Briggs register allocation approach in 2000 to be able to handle some specific irregularities (especially those present in the x86 architecture) such as more flexible multi-register usage. To handle this, they introduce the notion of a weighted interference graph (WIG), with weights assigned to nodes in the graph, e.g. based on register width. Instead of using the node degree to determine colorability like in the Briggs register allocator, they introduce a more complex heuristic for colorability based on these weights. Runeson and Nyström presented a similar approach to modifying graphcoloring register allocation in 2003 [16], also supplementing additional information to the interference graph, in their case by including a mapping of nodes to their respective register classes. As compared to Smith and Holloway, they also introduce generic "architecture description models" to be able to adapt their approach to different irregularities.

In 2002, Scholz and Eckstein [17] presented an approach which formalizes register allocation as a partitioned boolean quadratic optimization problem (PBQP) and uses dynamic programming in conjunction with heuristics to obtain register allocation solutions. Their approach focuses on highly irregular architectures which pose strong constraints on which registers can be used with which operations. The hypothetical highly structured register set they use to demonstrate their solution has separate address and index registers. A pairing between those types of registers determines which of them can be used in instructions together (e.g. a specific index register can only be used with a certain set of address registers).

However, these approaches focus specifically on handling irregularities based on requirements which always have to be satisfied, instead of the optional but desirable requirements we are concerned with when optimizing register allocation for compressed instruction sets.

## 3.2 Register Allocation and Code Generation for Compressed ISAs

Compressed instruction sets and the specific requirements they impose on code generation generally and on register allocation specifically have also been previously investigated. As described in the previous chapter, the original Thumb architecture was based on ARM and processors can support both instruction sets, but switching between Thumb and ARM requires an explicit mode change instruction.

Krishnaswamy and Gupta [18] presented an approach to allow for generation of mixed ARM and Thumb code in 2002 (note that this predates the Thumb-2 extension). It also includes a comparison of Thumb with regular ARM code regarding performance and size of the generated code, but focuses on rather coarse mixing of the instruction sets, meaning it either generates only Thumb or ARM instructions inside of a single function. Selection of whether to use compressed instructions is based on heuristic analysis of the code under consideration. Finer-grained mixing of instruction types inside of single functions is based on matching specific patterns in ARM code which are known to have shorter Thumb representations. These are selectively replaced by compressed instructions and surrounded by mode switch instructions.

Also based on the original Thumb without free instruction length intermixing, in 2005, the same authors Krishnaswamy and Gupta [19] presented a way to use the registers available in ARM by extending the Thumb ISA to allow the visible registers to be changed (of course requiring hardware modifications to support this). Their approach uses a custom extension of ARM/Thumb which adds SetMask instructions to choose which registers are visible without extending register specifiers in shortened

instructions. Registers are paired and only one of the paired registers is visible at any one time. To prevent code size penalties due to the SetMask instructions that need to be inserted, these instructions are coalesced into the following instructions where possible using their custom "Augmenting eXtensions" (AX) to decrease the number of additional instructions. Their work also includes an algorithm to place SetMask instructions in a way that reduces their overall number.

In 2010, Edler von Koch, Böhm, and Franke [20] presented an approach for code generation when allowing mixed 16- and 32-bit instructions, especially focusing on embedded use cases. The custom ARCompact ISA they investigate allows short and long instructions to be mixed without needing to modify the processor mode (the same way it is possible with the RVC extension). To leverage this, they introduce a method for "feedback-guided code generation", which is based on multiple compiler passes to improve code compression. The first compiler pass is used to annotate the intermediate representation (IR) with information on compression possibilities, and the following pass can use that information to deactivate generating compressed instructions where this would introduce additional move instructions or spills. They also include a code selection variant for "opportunistic" selection of compact instructions where requirements are incidentally fulfilled. As described in the previous chapter, a similar behavior is already present in the RISC-V toolchain due to the fact that the assembler already selects compressed instructions where all compression requirements are fulfilled. However, in the case of RISC-V, this behavior is transparent to the compiler itself and does not need any special support apart from utilizing the toolchain's assembler.

Lee, Moon, and Park [21] discuss another approach to designing compressed variants for instructions by grouping the full register set into multiple register banks. Their model works similarly to windowed register access concepts: Instead of defining one of the register banks as being available from compressed instructions, all registers can be made available by restricting the available registers to the currently selected bank. Their concept introduces a register allocation method which works with this design by grouping code into regions connected by sections of bank change and inter-bank copy instructions. Switching between banks is accomplished by adding a special register bank change instruction, which of course requires hardware support: For this, they proposed a "banked Thumb" (b-Thumb) instruction set. However, none of the architectures surveyed in the previous chapter use their proposed model to make more registers available for use with compressed instructions.

There are also works that address compressed instruction sets more generally: In 2016, Lopes et al. [22] presented a methodology for finding compression schemes for ISAs. It uses integer linear programming to optimize immediate value sizes in the compressed instructions, which they apply to design a compression extension for SPARC (which they call SPARC16). Their work also includes an analysis of different compressed ISA variants and evaluates the resulting compression ratios.

For our purposes, works that relate to the compression extension for RISC-V (RVC) are especially relevant: RVC has been thoroughly analyzed with regards to performance and code size. Li [23] also tries to further optimize RVC compression

results by reallocating the ISA namespace the RISC-V standard has assigned to compressed instructions. Perotti et al. [24] modify RVC with their *Xpulp* extension, which includes instructions to directly push values onto or pop values from the stack. They also survey compiler options that are useful to reduce code size, but do not introduce new compiler optimizations. These proposed schemes would all require adoption in the RISC-V ISA and hardware changes to be implemented.

Let us also review the current state of the art in mainstream optimizing compilers concerning code generation for compressed instruction sets, especially for RVC. In LLVM [25], this is handled during register allocation by exploiting register allocation order and register usage costs: The *greedy* register allocator included in LLVM includes a facility for specifying costs for using specific registers. These costs can be set in the backend description for each physical register. They are used to resolve allocation order by replacing the chosen register for a value with another, "cheaper" register in cases where there are no other interferences with values which would prohibit that [26]. In the case of Thumb-2 or RISC-V, only the registers which are part of the compressible subset are assigned no cost for using them [27], [28].

The result of the allocation is also dependent on the order in which registers are assigned. In the case of Thumb-2, there were documented changes to LLVM in order to optimize code size via adjusting the allocation order [29], [30]: With Thumb-2, the low registers R0 to R7 can be used for all compressed instructions, and these are currently also assigned first in LLVM: Previously, registers R12 and LR were assigned before R4 to R7. The proposed change [29] included an evaluation with a selection of benchmarks from SPEC CPU2000, SPEC CPU2006, and CoreMark, which documented an overall code size reduction of about 0.13 % in these benchmarks (most benchmarks showing a reduction in the range of 0.05 % to 0.4 %). Similar changes to the register allocation order in LibFirm were also implemented for this thesis. More details can be found in chapter 5.

However, to our knowledge, optimizing compilers like LLVM or gcc do not perform explicit modeling of compression requirements which goes beyond preferring compressible registers during allocation in this way, especially no modeling of other requirements such as 2-address requirements or multiple combined requirements.

## 3.3 Optimal Register Allocation

There are also methods that approach finding a solution for allocating registers in a specific program explicitly as generic optimization problems. These can be modeled e.g. by using integer linear programming, which allows solving them (possibly optimally) with suitable generic solving algorithms. Going this route usually allows requirements and parameters that impact register allocation to be more explicitly modeled in the problem statement than in fundamentally heuristic-driven approaches. It may also allow many other aspects of the register allocation problem to be modeled, such as requirements for instructions to be compressed. Arbitrary optimization metrics can in principle be inserted into the optimization problem and solved for. An example of a

recent comprehensive approach was presented by Lozano et al. in 2019 [31] as part of the Unison project [32]. Their work covers constraint modeling for register allocation combined with instruction scheduling and uses constraint solving to compute optimal register allocations. What makes this relevant in the context of this thesis is the fact that their solution also includes modeling of the costs and benefits of using compressed instructions. The requirements for instructions to be compressed can directly be included in the optimization problem that is built to describe a valid register allocation, e.g. when using code size as the overall cost function that is to be optimized for.

However, optimally solving register allocation in this way is usually only suitable in specific situations due to compilation performance concerns. Lozano et al. demonstrate speedups and code size improvements with their approach finding optimal solutions in cases of up to around 1000 instructions (given a fixed time limit of 15 minutes for finding a solution). They also concede that this approach is only applicable in cases where generated code performance or size is particularly important to warrant the trade-off with compilation times that are considerably longer than with heuristic-based approaches.

# **4** Compression Optimization

This chapter describes how our optimization is designed and how it is integrated into the copy optimization heuristic in LibFirm to accomodate compression requirements. It also contains an overview of how the implementation is handled in the LibFirm codebase.

The design consists of several parts that have to be in place. We will discuss them in turn: Considerations about the requirements for the proposed solution are outlined in the first section 4.1. To be able to take compression into account during register allocation, we need to be able to tell the register allocator in the backend which instructions in the lowered graph have compressed variants, and which requirements have to be satisfied in order for them to be used. This is discussed in section 4.2. This information can then be used in the copy optimization heuristic to adjust the result in a way that improves compression, but does not negatively affect the quality of the register allocation. This is especially relevant in case no compression information is provided by the backend. This part will be described in more detail in section 4.3. Notes on how the optimization can be implemented for backends can be found in section 4.4.

## 4.1 Design Requirements

This section serves as a high-level overview over how the extension of LibFirm for compression-aware register allocation is designed, especially focusing on which requirements guide the design. Let us look at the basic requirements the optimization should meet:

• Not all architectures supported by LibFirm make use of compressed instructions. This means that our optimization is not relevant for all target architectures, but only useful for certain backends. Compression only affects the goals of register allocation in detail while the basic target of eliding as many copy instructions as possible remains the main focus of the heuristic. In order to avoid duplicating existing copy optimization code by creating a new compression-aware register allocator, we want to design the optimization as a backwards-compatible extension to the existing heuristic. This enables backends to opt into the optimization where applicable. At the same time, our optimization should not affect the results of register allocation in other cases (e.g. for architectures without compressed instructions).

Introducing multiple distinct code paths for compression-aware and -unaware register allocation should also be avoided to not impede maintainability: They

may diverge and fixes or performance improvements would have to be duplicated. Introducing an explicit new subsystem that handles register allocation for compressed instructions sets may also complicate testing of the register allocator.

- When including compression handling in the existing register allocation step, the execution time of the register allocator should also not be affected in cases where the backend being used does not support compression or no compression-related information is available. Preferably, this should be handled without needing an explicit flag that disables compression-aware register allocation where it is not applicable in order to preserve performance for this case.

- In the register allocation architecture used in LibFirm, the result of the copy minimization step in general has large performance implications for the generated code. It directly affects the number of copy instructions which need to be executed.

In contrast, the effects of compression are more specifically related to code size, which is only indirectly linked to code performance (e.g. due to instruction caching; for more considerations about this, see chapter 5). For this reason, compression optimization should in most cases not trade off copy instructions versus compressed instructions, but instead prioritize eliding copy instructions where possible.

- The optimization itself should be independent of a specific backend. As described above, this allows backends to opt into using it: They should only need to specify their requirements for compressed instructions. This information can be provided in their architecture specification and by implementing a clear interface to the register allocator.

- The optimization should not alter the basic approach of register allocation used in LibFirm and be integrated into the concepts already used here: The welltested copy optimization heuristic based on chunk-recoloring that is operating on affinity graphs.

On account of these goals, the compression optimization described in this thesis uses the metrics and capabilities already present in the existing heuristic and refines them to include added information pertaining to compressibility of the generated code. Specifically, this applies to the *weight* of edges in the affinity graph and *costs* for not fulfilling specific affinities: These are adjusted and extended, but the basic principle of finding a suitable register allocation result remains untouched. That also means that the result for a certain configuration of affinity and interference graphs, edge weights, and associated costs remains unchanged.

## 4.2 Compressibility Specification

During execution of the copy optimization heuristic, information about compression opportunities and the corresponding register requirements needs to be available. This is highly backend-specific: Different ISAs vary in which compressed instruction variants are available and which requirements they each have. For the purposes of this thesis, the model at least needs to cover the types of requirements that are present for RISC-V, but it should be designed in a way that is sufficient for other similar instruction sets as well. This way, compression-aware register allocation support can be easily added for other instruction sets like Thumb.

In general, LibFirm's register allocation is abstracted from specific backends. It relies on register-specific information that is part of a well-defined interface between the backend and the register allocator. This also covers required information concerning spilling of values (which is performed as the compiler step before). We extend this interface to also cover information related to code compression. Without the compression optimization, it already includes the following information:

- The costs associated with spills and reloads of values along with references to functions that insert the nodes required to perform them into an IR graph are directly included in the interface.

- A description of available registers and instructions as well as associated metadata is part of what we will call *architecture* or *backend specification*. They are implemented in Perl syntax as a way to provide a more compact representation of the specification. Perl scripts take these as input and generate C source code containing information about each register, available instructions, and register requirements for their input and output.

The register description also contains a list of which registers are included in each available register class. For each register, other associated information such as its name or the index it is encoded with in instructions is also included.

As described in section 2.2, compressed instructions from RVC may have two fundamental types of requirements for the register placement of operands or results: Requirements of values to be placed in the subset of compressible registers and 2-address requirements. We will discuss how each one of them is integrated into the heuristic in more detail in section 4.3, but will first cover which compression information is required to represent this and how it can be specified in the backend. Information about compression requirements exists on two levels:

**Compressible register subset** On the level of the register set, we need to specify the *compressible register subset*. This means that each register needs information associated with it about whether it is part of this subset. We will also refer to those registers in the subset as *compressible* registers. They are specified by adding a flag to all compressible registers.