Institut für Programmstrukturen und Datenorganisation (IPD)

Lehrstuhl Prof. Dr.-Ing. Snelting

# Synthesising Instruction Selection

Masterarbeit von

### Andreas Fried

an der Fakultät für Informatik

Erstgutachter:Prof. Dr.-Ing. Gregor SneltingZweitgutachter:Prof. Dr. rer. nat. Bernhard BeckertBetreuender Mitarbeiter:Dipl.-Inform. Sebastian Buchwald

Bearbeitungszeit: 17. Februar 2016 – 8. August 2016

# Zusammenfassung Abstract

In dieser Arbeit wird ein Tool vorgestellt, das die Befehlsauswahlphase eines IRbasierten Compilers automatisch generieren kann. Aus formalen Spezifikationen der Zwischensprache des Compilers und der Ziel-Maschinensprache findet es mittels eines SMT-Solvers zu jeder Maschineninstruktion einen äquivalenten DAG in der Zwischensprache. In der Spezifikation kann insbesondere auch Speicherzugriff effizient dargestellt werden. Aus den so gewonnenen Zuordnungen wird dann eine Befehlsauswahlfunktion generiert, die in FIRM integriert werden kann. Sie ist wie die bestehende FIRM-Befehlsauswahl ein "greedy DAG-matcher".

Die Synthese von 58 Maschinenbefehlen aus einer Zwischensprache mit 20 Befehlen dauert 2 Stunden. Die synthetisierte Befehlsauswahlfunktion kann die Mehrzahl der Befehle aus dem SPEC-CINT2000-Benchmark in Maschinensprache übersetzen.

We present a tool that can automatically synthesise the instruction selection phase of an IR-based compiler. Using formal specifications of intermediate representation and machine language instructions, we match machine language instructions to DAGs of IR instructions using an SMT solver. Our specification model includes an efficient representation of memory access. From the associations between IR and machine language, we generate a greedy DAG-matching instruction selector that can integrate into FIRM.

Our tool can synthesise an instruction selector for 58 machine instructions from a set of 20 IR instructions in 2 hours. The synthesised instruction selector is able to handle the majority of instructions from the SPEC CINT2000 benchmark.

# Contents

| Intro  | oduction                                                                                                                                                     | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Basics |                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2.1.   | Compiler Design                                                                                                                                              | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2.2.   | SMT                                                                                                                                                          | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2.3.   |                                                                                                                                                              | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Desi   | gn and Implementation                                                                                                                                        | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3.1.   | Modelling Instructions                                                                                                                                       | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3.2.   | Synthesis Algorithm                                                                                                                                          | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3.3.   | Optimisations                                                                                                                                                | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3.4.   | Generating the Instruction Selector                                                                                                                          | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Eval   | uation                                                                                                                                                       | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4.1.   | Synthesis Performance                                                                                                                                        | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4.2.   | IR Coverage                                                                                                                                                  | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4.3.   | Replacing the Instruction Selector                                                                                                                           | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4.4.   | Specification and Synthesis                                                                                                                                  | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4.5.   |                                                                                                                                                              | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4.6.   |                                                                                                                                                              | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Con    | clusion                                                                                                                                                      | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5.1.   | Limitations                                                                                                                                                  | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5.2.   | Further Work                                                                                                                                                 | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5.3.   |                                                                                                                                                              | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Арр    | endix                                                                                                                                                        | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|        | Basi<br>2.1.<br>2.2.<br>2.3.<br>Desi<br>3.1.<br>3.2.<br>3.3.<br>3.4.<br>Eval<br>4.1.<br>4.2.<br>4.3.<br>4.4.<br>4.5.<br>4.6.<br>Cont<br>5.1.<br>5.2.<br>5.3. | 2.1. Compiler Design         2.2. SMT         2.3. Related Work         3.4. Modelling Instructions         3.4. Generating the Instruction Selector         3.4. Generating the Instruction Selector         4.1. Synthesis Performance         4.2. IR Coverage         4.3. Replacing the Instruction Selector         4.4. Specification and Synthesis         4.5. Code Quality         4.6. Performance of the Instruction Selector         4.6. Performance of the Instruction Selector         5.1. Limitations |

### 1. Introduction

The point of modern programming is not to convey orders to a computer, but ideas to a fellow human. For this reason, computer science has developed high-level programming languages, which are easier for humans to write and to understand.

Of course, a computer cannot execute a program in a high-level language without help. A translation program called a *compiler* turns the high-level program into a machine code program, which the computer can execute. In addition, the compiler should automatically improve (*optimise*) the program, so that the developer may concentrate on writing clear and understandable code, but still achieves good performance.

We can see from these requirements that developing a good compiler is a substantial undertaking. The major compilers GCC and LLVM each have hundreds of thousands of lines of code, and have been in development for more than 10 years. In fact, most of the code and development effort went into the optimisations, which are in principle the same in every compiler. Therefore, modern compilers are designed in such a way that the optimisations (*middle end*) can work together with any high-level language (*front end*) and any machine language (*back end*).

The middle end uses its own *intermediate language* to represent programs independently from the front end language, and more or less independently from the back end language (GCC's intermediate language is more backend-specific than LLVM's). This means that the front end has to translate the high-level language to the intermediate language, and the back end has to translate the intermediate language to the machine language. It is the second of these translation steps that this present work deals with.

In order to use the machine as efficiently as possible, the compiler should of course make use of all its capabilities, i.e. it should be able to use the whole machine language. This requires a lot of work, because today's machines (first and foremost Intel's) have very large *instruction sets*, and frequently extend them. A good compiler needs to keep up with this development.

To add a new machine instruction to a compiler, a developer has to do the following: Translate the new instruction to intermediate language, check if the translation overlaps with existing ones, write code to find the translation in an intermediate language program, and finally write code to generate an instance of the new instruction where its translation is found. With our work, we aim to relieve compiler developers of this tedious task.

In our approach, the developer just has to specify the behaviour (*semantics*) of each instruction in the intermediate and machine language in an abstract way. From these descriptions, we automatically generate the translation step from intermediate language to machine language (called *instruction selection*). This works even when the same behaviour is specified in two different ways. For example, it is not obvious that the expressions  $\sim (-x)^1$  and x - 1 are equivalent, but our program will match instructions even in these cases.

In our work, we use an *SMT solver*. This is a software tool that can automatically find the solutions to certain simple kinds of mathematical and logical problems. For example, we may ask it to find integers x > 0, y > 0, and z > 5 such that  $x^2 + y^2 = z^2$ , and the SMT solver will find one solution (it might be x = 16, y = 12, z = 20).

However, even with such a powerful tool at our disposal, there remains work to be done, which we present in this thesis. First, we look at some prerequisites at more detail in Chapter 2. Chapter 3 is the main part of our work; we develop our algorithm to synthesise instruction selection. In Chapter 4, we then evaluate the performance of our algorithm from different perspectives. Finally, we discuss our results and take a broader outlook in Chapter 5.

<sup>&</sup>lt;sup>1</sup>" $\sim$ " refers to the function that flips all bits in its argument

## 2. Basics

### 2.1. Compiler Design

At the most basic level, a compiler's task is to translate a program written in a source language to a semantically equivalent program in a target language. Besides that, the output program should be optimised, for example to run as quickly as possible, or to be as small as possible. The compiler therefore applies *optimisation passes* to the program when translating it, for example removing redundant code or simplifying computations.

A compiler usually includes a large number of optimisation algorithms, each of which requires considerable development effort. Compiler developers therefore want to share optimisations between compilers for different languages. Moreover, neither source nor target language are usually designed to be easily manipulated programmatically, so that a more convenient representation is required anyway.

For these reasons, most compilers are designed around an *intermediate representation* (IR), on which most parts of the compiler operate. We will discuss IR design in more detail in Section 2.1.1. A compiler having an IR is usually divided into three components, which process the source program in turn:

- First, the source-specific *front end* parses the source language program and checks it for errors. If the program is correct, the front end converts it to the compiler's IR.

- Next, the *middle end* applies the optimisations to the IR program in order to produce an efficient output program.

- The optimised IR program is finally passed to the target-specific *back end* of the compiler, where the IR is transformed into the target language, and some additional optimisations may be performed.

By way of the middle end, every front end can be combined with every back end. However, the compiler now requires two translation steps, from source language to IR, and from IR to target language. The latter transformation is the *instruction selection*, which we describe in Section 2.1.3.

From here on, we shall assume the most common case for compiler construction, namely that the source language is a high-level imperative programming language, and that the target language is an assembly language for a particular processor.

| f:       |               |  |  |  |

|----------|---------------|--|--|--|

| movl     | 8(%esp), %eax |  |  |  |

| testl    | %eax, %eax    |  |  |  |

| je       | .LBB0_2       |  |  |  |

| movl     | 4(%esp), %ecx |  |  |  |

| addl     | %ecx, %ecx    |  |  |  |

| subl     | %ecx, (%eax)  |  |  |  |

| .LBB0_2: |               |  |  |  |

| retl     |               |  |  |  |

(b) x86 assembly produced by clang with optimisations enabled

- define void @f(i32 %a, i32\* %b) #0 {

%1 = mul nsw i32 2, %a

%2 = icmp ne i32\* %b, null

br i1 %2, label %3, label %6

; <label>:3

%4 = load i32, i32\* %b, align 4

%5 = sub nsw i32 %4, %1

store i32 %5, i32\* %b, align 4

br label %6

; <label>:6

ret void

}

- (c) LLVM bitcode after load-store optimisation

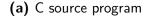

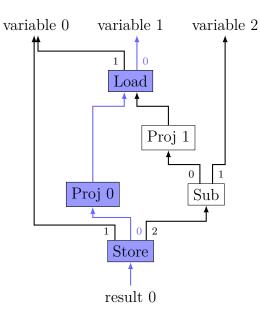

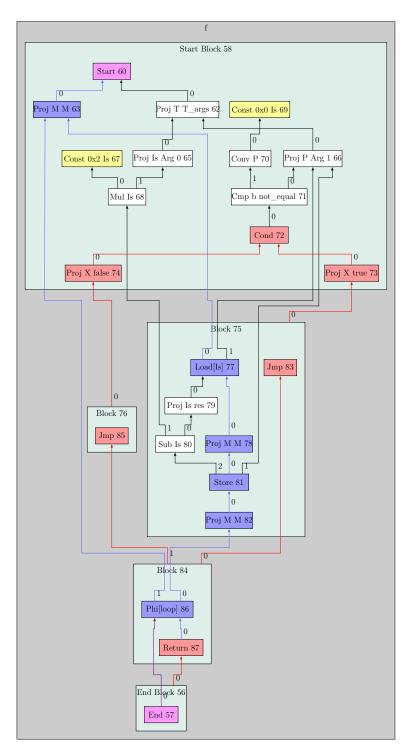

(d) FIRM graph before optimisation. See page 76 for a larger version.

**Figure 2.1.:** Comparison of high-level, assembler and intermediate languages. Both high-level and assembler language are more concise, but IRs have less complexity.

### 2.1.1. Intermediate Representations

We have already presented the reasons for using an IR. In order to motivate the design choices involved in an IR, we will first look at the typical structure of source and target languages (i.e. high-level and assembly languages), and see why they are unsuitable as IRs.

Throughout this section, we will refer to the example programs in Figure 2.1. Figure 2.3c shows a sample C program, the others show its translation into x86 assembly (Figure 2.1b), LLVM bitcode as an example for an IR (Figure 2.1c), and FIRM (Figure 2.1d). We will discuss FIRM in more detail in Section 2.1.2.

Programs in high-level languages are composed of nested statements and expressions. They are internally represented as an abstract syntax tree (AST), annotated with types and symbol resolutions. The AST can have tens of different node types, each with a different internal structure. For example, the grammar for C99 has 21 non-terminal symbols for expressions, 35 for declarations and 9 for statements. [1, Annex A]. This makes it inconvenient for the compiler to analyse and manipulate the AST. In addition, the language might have some abstract concepts, which are present in the AST, but hard for the optimisation algorithms to deal with.

On the other hand, assembly language programs have a simpler structure; they are lists of atomic<sup>1</sup> instructions. However, matters are complicated by hardware limitations: There are only a fixed number of registers available, and instructions might have implicit side effects (e.g. modifying flags). In addition, CISC processors often have instructions that combine several simpler instructions into one. Thus, the instruction set can become quite redundant. Again, such a language is not suited for analysis and manipulation by a compiler.

Having these problems in mind, we can now draw up the criteria for IR design.

- **Simple structure** The structure of the IR should be simple and uniform, so that it may be easily handled by the compiler.

- **Small size** There should be a small number of instructions with simple semantics in the IR to ease analyses in the middle end. However, it should be reasonably easy for the front end to produce IR from the source language.

- **Regularity** IR instructions should have as few special cases as possible, and should not have implicit side effects.

- **Abstraction** The IR should abstract from details of both the hardware and the source language.

Following these guidelines, IRs traditionally have the same structure as machine languages: They consist of sequences of atomic instructions. An IR's instructions are mostly simple: It usually contains instructions for every basic arithmetical and logical operation, and separate instructions for memory access.

<sup>&</sup>lt;sup>1</sup>i.e. "indivisible", not "suitable for synchronisation"

On the other hand, it also contains some high-level instructions, which can be equivalent to a long sequence of machine instructions. For example, a function call is often represented as a single IR instruction in order to abstract from the particular hardware mechanisms in use.

Another important point of difference between IRs and machine languages is the treatment of registers. A processor has a limited register set, which the compiler's back end must carefully manage. This *register allocation* is a complex problem, and the middle end should not have to deal with it.

### SSA form

Modern IRs use *static single assignment form* (SSA form) [2] to represent values that the high-level language would keep in local variables, and the machine language would keep in registers. In SSA form, each IR instruction *defines* some SSA values and *uses* SSA values previously defined. To use an SSA value, an instruction refers to the instruction that defined it earlier. Since SSA values are immutable, each assignment to a variable creates a new SSA value. The variable is therefore represented by a sequence of SSA values, with one SSA value for each assignment to it.

SSA form requires some overhead to deal with control flow. First, the program is divided into *basic blocks*. Simply put, a basic block is the sequence of instructions from one jump or jump target to the next, i.e. a set of instructions that are always executed together.

If a basic block B has multiple *predecessors*, i.e. basic blocks that jump to it, some values may depend on which predecessor actually executed before B. To express this dependency, SSA form uses  $\phi$ -functions at the start of the basic block. The  $\phi$ -function's takes the values from the predecessors as arguments and returns the value from the predecessor that actually executed. See Figure 2.2 for an example, whereby the value of **x3** depends on whether block A or block B executed previously.

In spite of this overhead, SSA form is easily constructible [3], and greatly simplifies later analyses, because there is no need to track the value of local variables.

### 2.1.2. The Firm IR

Even though IRs traditionally represent programs as a sequence of instructions, such total ordering is unnecessary. Instructions that do not use each other's results or have side effects can be reordered without changing the program's semantics. If the instructions are not fully ordered, the compiler can manipulate the program more easily.

FIRM implements the idea of partially ordering instructions by representing programs as *dependency graphs*. In a dependency graph, each instruction becomes a node, and each dependency between instructions becomes an edge from the dependent instruction to the instruction it depends on. if (condition()) if (condition()) /\* block A \*/ { /\* block A \*/ { x = 1;x1 = 1;} } else else /\* block B \*/ { /\* block B \*/ { x = 2; $x^2 = 2;$ } }  $x3 = \phi(x1, x2);$ return x; return x3; (a) C program (b) Program in SSA form

**Figure 2.2.:** An example for the use of  $\phi$ -functions. Part (a) shows a code snippet in C, part (b) shows the same code in SSA form. The value of x3 depends on previous execution. The  $\phi$ -function selects the value form the predecessor block that executed.

### Dependencies

Generally speaking, an instruction i depends on another instruction j, if i requires information from computed by j, and must therefore execute after j.

This includes the information, whether i should execute at all. In this case, i has a *control dependency* on j. For our work, *data dependencies* are more important though, and we shall now discuss these in more detail.

The simplest data dependency is the *define-use relationship*. The instruction j is in define-use relationship with the instruction i, if i uses a value that j has previously defined. This is the usual dependency between arithmetical instructions.

Besides that, instructions can also be data dependent through memory: If the instruction i reads a value from a memory location that j writes to (read-after-write), i and j must not be reordered to preserve the program's behaviour. The same is true for write-after-write and write-after-read dependencies.

Define-use relationships are explicit in all SSA-based IRs, but data dependencies through memory side-effects are only kept implicitly in the total order of the instructions. FIRM makes all data dependencies explicit, and can therefore do away with ordering instructions totally.

A FIRM instruction that has side-effects uses and defines an M-value, which represents the state of the outside world at a given position in the program. Thus, instructions with side-effects are ordered by a chain of M-values from one to the next.

The M-value also represents the state of memory (hence its name), and we will mostly need this aspect of it in our work below.

Ignoring loops, the dependency relation is a partial order, and the dependency graph is therefore a DAG. Only  $\phi$ -instructions in loops may break the partial order

to use a value defined in the previous iteration. Since we will not be concerned with  $\phi$ -instructions in our work, we may treat the dependency graphs as DAGs.

### Modes

Each FIRM node has a *mode*, which determines the kind of result it produces. It may also determine the kinds of arguments the node takes.

In contrast to types, which the programmer or the programming language define, modes are defined by the compiler. FIRM has signed and unsigned integers 8, 16, 32, and 64 bits wide; boolean values; pointers; single- and double-precision floating point values; and special internal modes, namely M-values, values representing control flow, and tuples.

Compilers using FIRM map primitive types of their source languages to the respective modes, and represent compound types as pointers.

The tuple mode T is required for nodes that define multiple values. For example, a Call node, which represents a procedure call, returns both the call's return value and the updated M-value in a tuple.

Nodes that use one of the values in a tuple do so by way of a *projection* node (called Proj). The Proj node uses the tuple value and defines the value of one of its elements.

### **Firm Nodes**

Let us now take a closer look at how FIRM implements these principles. A FIRM node has the following components: Firstly, an *opcode* specifies the kind of instruction that the node represents, and the node's mode may specify a variant (e.g. floating-point or integer arithmetic).

The node's dependencies are stored in an array of pointers to the nodes it depends on. Because the dependencies of arithmetical instructions are their arguments, dependencies are also called arguments or inputs when talking about FIRM nodes.

Finally, a node may have some opcode-specific *attributes*. For example, a node defining a constant value (a "Const" node) has this value as an attribute.

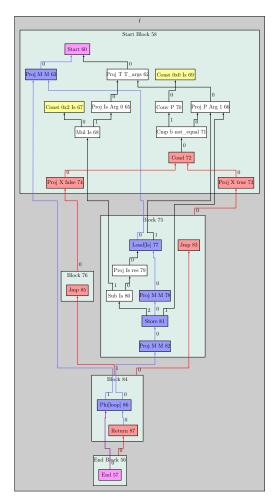

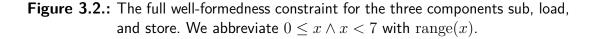

We shall now give an overview of the most important typed of FIRM nodes. See Figure 2.3 for a display of some common nodes. The full list of available nodes can be found in the FIRM API [4].

**Arithmetical nodes** All usual arithmetical and logical operations are available in FIRM. The operations are not variadic, each instruction takes one or two arguments. Arithmetical instructions can have all integer modes, and floating-point modes where applicable. The input(s) must have the same mode as the output. A conversion instruction (Conv) is available to convert between modes.

Instructions that may fail (namely division and remainder) additionally depend on and produce an M-value to capture the side effect of them failing.

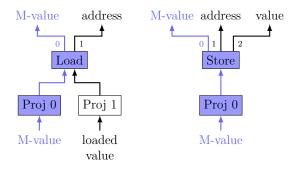

- **Memory-access nodes** Only two kinds of nodes are relevant for our work, namely Load and Store. Both have the expected semantics. Even though Load nodes do not change the contents of memory, they still define a new M-value. This is required to encode write-after-read dependencies, and to model access to volatile memory.

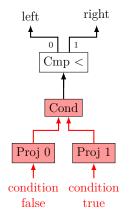

- **Control flow** FIRM models control flow by giving basic blocks (and therefore the nodes contained in them) a dependency on a control flow value produced by a jump node. There is a Jmp node for unconditional jumps and a Cond node, which takes a boolean value and produces a tuple of two control flow values, one of which is chosen by the argument.

The Cond node usually works together with a Cmp (compare) node, which compares two values and produces a boolean value as its result. The relation to use ( for integral modes:  $\langle, \leq, \neq, = \geq, \rangle$ ) is an attribute of the Cmp node.

### 2.1.3. Instruction Selection

The compiler back end transforms IR to machine language in three main steps, of which instruction selection is the first. Its task is only to replace IR instructions with matching machine language instructions while keeping the program in graph form. In later phases, the instructions are fully ordered (*scheduling*), and hardware registers are assigned to the SSA values in the program (*register allocation*).

One machine instruction usually subsumes several IR instructions. Therefore, each machine instruction is associated with an IR graph pattern that it implements. A graph pattern is an incomplete IR graph, where some inputs are left unspecified (the pattern's arguments) and some nodes are marked as results. The unspecified inputs correspond to the inputs of the machine instruction, and the marked result nodes correspond to its results. If the machine instruction and its pattern are given the same inputs, they produce the same results. Therefore, the instruction selector can replace an occurrence of the pattern within the IR graph with the machine instruction.

Additionally, each machine instruction is assigned a cost, for example the estimated number of cycles it takes to execute.

The task of instruction selection is then to cover the input IR graph with the patterns given by the available machine instructions, such that every node is covered by one pattern, and the edges within the patterns correspond to edges present in the graph. Also, in order to produce efficient machine code, the total cost of all instructions used should be minimal.

Unfortunately, this covering problem is only tractable if the IR graph is a tree. Even if we do not account for loops and restrict ourselves to IR DAGs, the problem becomes NP-complete [5]. Therefore, a large number of heuristics and formalisations have been developed. Blindell presents an extensive survey of instruction selection algorithms in [6].

### (a) Examples for arithmetical and bitwise nodes.

(b) Memory access nodes with their Projs.

- (c) A Cmp node and a Cond node as used for conditional jumps. In this case, the jump is taken if left < right.

- Figure 2.3.: Some common FIRM nodes. For the full list of available nodes, see the API [4].

We generate a greedy DAG-matcher, which recursively traverses the input dependency graph. At each node, it finds the largest pattern that has the node as a root, and replaces that pattern with the associated machine instruction.

However, our work can be applied to any instruction selector. Our task is to provide the associations between IR patterns and machine instructions. From this information, any kind of instruction selector can be built.

### 2.2. SMT

SMT (Satisfiability Modulo Theories) is an extension of boolean satisfiability (SAT). In it, the boolean variables of a SAT problem may be replaced by terms from one or more *theories*.

An SMT theory defines a sort (i.e. a type) or family of sorts together with its associated operations. The SMT-LIB project has standardised some SMT theories [7], which are used by the major SMT solvers. We now give an overview of the theories that we use in our work below.

First, SMT-LIB treats classic SAT as a theory named "Core". This theory defines the sort **Bool** with its values **true** and **false** and the usual logical operations.

The "Int" theory defines the sort **Int** of unbounded integers together with the usual arithmetic operations and the usual ordering.

The "FixedSizeBitVectors" theory defines a family of sorts: For each n, there is a sort  $BitVec_n$  representing a vector of n bits. The theory defines the usual logical operations on the bits, as well as operations to concatenate vectors and extract sub-vectors. More importantly, the theory also defines arithmetical operations, which interpret the bit-vectors as integers encoded in binary form. The FixedSizeBitVectors theory is therefore useful to represent CPU arithmetic.

Finally, the "ArraysEx" theory defines maps from one type to another. It also defines two operations to manipulate these maps: A value can be associated with another one by *storing* the association in the map, and the value associated with a given value can be *selected* from the map. These maps can be used to represent memory as a map from addresses to their contents.

In addition to theories, SMT problems also allow first-order quantifiers. As with SAT problems, free variables are implicitly existentially quantified, and the SMT solver needs to produce a valid assignment to them, called a *model*.

We use the SMT solver Z3 [8] in our work, which supports all these theories, and allows to mix them in one query.

In the algorithms below, we will use the following convention to represent SMT queries, with all quantifiers made explicit:

$(r, a) \leftarrow \text{SMTSOLVE}(\exists x.\phi(x))$

The function returns a pair, whereby the first element is either **sat** (satisfiable) or **unsat** (unsatisfiable), and the second element gives a model for the existentially quantified variables if the formula was satisfiable. We represent the model as a function from a variable's name to its assigned value.

For example, if we execute this query:

$(r, a) \leftarrow \text{SMTSOLVE}(\exists x. \exists y. \exists z. x * x + y * y = z * z),$

we have r = sat and a(x) = 3, a(y) = 4, a(z) = 5 (or another Pythagorean triple).

### 2.2.1. Limitations

An SMT problem that may freely use quantifiers and the theories presented above can be undecidable, because both first-order logic [9] and non-linear arithmetic [10] are undecidable. Therefore, the admissible SMT problems may be restricted with a certain *logic*. For example, the logic might forbid non-linear arithmetic, the use of quantifiers, or unbounded integers (using bit vectors instead).

However, even if an SMT problem is decidable, it may still be impractically hard to solve. For example, a bit vector problem involving a universally quantified variable is decidable, but it may be necessary to consider all possible cases. When the bit vector becomes sufficiently large, this is clearly too inefficient.

Therefore, the problems given to an SMT solver should be as simple as possible, and should avoid universal quantification. However, a universal quantifier can sometimes be eliminated by breaking up one intractable SMT problem into several smaller ones.

### 2.2.2. CEGIS

CEGIS (Counterexample-guided inductive synthesis) can eliminate the universal quantifier in formulae of the structure  $\exists x. \forall y. \phi(x, y)$ , where  $\phi(x, y)$  is a quantifier-free SMT formula.

In principle, the SMT solver now needs to consider all cases for y. However, a few cases are usually enough to check those formulae which occur in practice. If  $\phi$  is sufficiently benign, there is a small set  $\{y_1, \ldots, y_n\}$  such that

$$\exists x. \phi(x, y_1) \land \ldots \land \phi(x, y_n) \Rightarrow \forall y. \phi(x, y)$$

CEGIS (Algorithm 1) is an iterative heuristic to find this set of useful *test cases*. In one iteration, CEGIS first queries the SMT solver for an  $x^*$  that satisfies  $\phi$  for all current test cases. This is called the *synthesis* step. Next, the algorithm queries for a  $y^*$  that does not satisfy  $\phi(x^*, y^*)$  (*counterexample* step). If the solver finds a model for  $y^*$ , it is added to the set of test cases. Otherwise, the model for  $x^*$  satisfies  $\phi$  for all  $y^*$ .

### 2.3. Related Work

### 2.3.1. Superoptimisers

The algorithm we present in Chapter 3 is closely related to those used in superoptimisation. Given a loop-free input program, the goal of superoptimisation is to find the shortest program equivalent to the input. Thus, a superoptimisation algorithm

### Algorithm 1 CEGIS

```

1: procedure CEGIS(\exists x. \forall y. \phi(x, y))

2:

Y \leftarrow \emptyset

3:

loop

(r_1, a_1) \leftarrow \text{SMTSOLVE}(\exists x^* \land \land y_i \in Y \phi(x^*, y_i))

4:

if r_1 = \text{unsat then}

5:

6:

return (unsat, \emptyset)

end if

7:

(r_2, a_2) \leftarrow \text{SMTSOLVE}(\exists y^*. \neg \phi(a_1(x^*), y^*))

8:

if r_2 = unsat then

9:

return (sat, {x \mapsto a_1(x^*)})

10:

else

11:

Y \leftarrow Y \cup a_2(y^*)

12:

end if

13:

end loop

14:

15: end procedure

```

has two parts: it needs a way of generating possible programs, and it needs a way to check whether two programs are equivalent.

Superoptimisation was introduced by Massalin in 1987 [11] with the Superoptimizer. The Superoptimizer enumerates all programs as lists of machine instructions, and checks them for equivalence with the goal using a suite of random tests. A complete equivalence check was intractable at the time due to insufficient computing power.

In 2011, Gulwani et al. presented an algorithm which makes it possible to use SMT solvers for automated program synthesis [12]. They represent loop-free programs as a DAG of *components* and encode both the search and the verification in SMT queries. Thus, manual enumeration of all programs becomes unnecessary. This algorithm was used by Collingbourne to build the LLVM superoptimiser Souper [13].

### 2.3.2. Specifying Instruction Selectors

Since machine instructions often have multiple similar variants, and compiler developers want to avoid code duplication, some compilers contain a domain specific language to describe machine instructions concisely. For example, GCC contains "machine descriptions" [14], and LLVM uses the "TableGen" format [15]. Preprocessing tools then take these descriptions of the target instruction set, and expand them into source code (e.g. datatype definitions and parts of the back end).

These instruction specifications also contain an IR pattern for the instruction. However, this is a purely syntactic description. The generated instruction selector will only be able to match exactly the specified pattern. In contrast, we describe the instructions semantically, and can also find patterns that have a structure different from the specification.

### 2.3.3. Other Synthesis Approaches

Dias and Ramsey have already presented a tool to generate instruction selectors [16]. However, their synthesiser finds a sequence of machine instructions for each IR instruction, thus producing inefficient back end code. The authors claim that this can be remedied by subsequent peephole optimisations.

Heule et al. also worked on synthesis in the context of machine languages [17]. They developed a tool to find logical formulae for x64-64 instructions through inference from the instructions' behaviour in experiments.

### 3. Design and Implementation

In this chapter, we describe the design of the instruction selection generator, and of the algorithms it uses.

The instruction selection generator takes the semantic models of both IR and machine instructions, and produces code implementing an instruction selector that translates the IR to the machine language.

Algorithm 2 gives an overview of the process. The parameter I is the multiset of IR instructions, and M is the set of machine instructions. I must contain each IR instruction in sufficient number to build a pattern for any machine instruction.

For each machine instruction (the goal instruction), the synthesiser produces a set of patterns of IR instructions, which we collect in the set S. Then, the code generator creates an instruction selector based on this set.

### **Algorithm 2** Overview

| 1: <b>procedure</b> SELECTIONGENERATOR $(I : \{\{\text{Instruction}\}\}, M : \{\text{Instruction}\}\}$ |                                                               |  |  |  |

|--------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|--|--|--|

| 2: $S \leftarrow \{\}$                                                                                 | $\triangleright S : \{(M \times \operatorname{Pattern}(I))\}$ |  |  |  |

| 3: for each $g \in M$ do                                                                               |                                                               |  |  |  |

| 4: $\{p_1, \ldots, p_n\} \leftarrow \text{Synthesise}(I, g)$                                           | $\triangleright p_i : \operatorname{Pattern}(I)$              |  |  |  |

| 5: $S \leftarrow S \cup \{(g, p_1), \dots, (g, p_n)\}$                                                 |                                                               |  |  |  |

| 6: end for                                                                                             |                                                               |  |  |  |

| 7: $c \leftarrow \text{GENERATECODE}(S)$                                                               | $\triangleright c$ : source code string                       |  |  |  |

| 8: return $c$                                                                                          |                                                               |  |  |  |

| 9: end procedure                                                                                       |                                                               |  |  |  |

As we have pointed out in Section 2.1.3, the results of the synthesiser can be used for any instruction selection algorithm. For compatibility with FIRM, we generate a greedy DAG-matcher as used in the existing FIRM back ends.

We present both steps in more detail below (Section 3.2 and Section 3.4). However, we first need to describe how we model instructions and their semantics (Section 3.1).

### **Notes on Notation**

We will use the usual mathematical operators for both bit-vectors and integers. In addition, we use these bit-vector-specific functions:

- $v[n \dots m]$ : The extraction of bits n down to m from the bit-vector v

- $v[b \mapsto x]$ : A copy of bit-vector v with the bit at index b set to x

•  $u \circ v$ : The concatenation of bit-vectors u and v.

The indices are zero-based, with bit 0 being the least significant bit. For example, 0110[2...1] = 11,  $0110[1 \mapsto 0] = 0100$ , and  $11 \circ 0100 = 110100$ .

We also use square brackets to denote literal lists and access to list elements, as is common in programming. Lists use zero-based indexing, too.

Finally, we use let-bindings as known in functional programming to make our expressions more readable: We define "let x = t in  $\phi$ " to mean  $(\lambda x. \phi)t$ , where the abstraction captures unbound occurrences of x in  $\phi$ .

### 3.1. Modelling Instructions

Our goal in this section is to construct a model of IR and machine instructions to represent them in SMT formulae. Our model is an extension of the one presented by Gulwani et al. [12].

Basically, an instruction takes some *arguments*, and computes some *results*. In addition, some instructions have *internal attributes*, which are chosen at compile time and fixed at run time. For example, a conditional branch instruction has the condition code as an internal attribute. Together, these form the instruction's *interface*.

The instruction declares the sorts of its interface in three lists  $S_a$ ,  $S_i$ , and  $S_r$  for arguments, internal attributes and results respectively.

We also have to specify the instruction's *behaviour*. We do this through three functions P, Q, and V. Each of the functions takes three lists of SMT expressions  $v_a$ ,  $v_i$ , and  $v_r$ , whereby the sorts of these expressions must be equal to those in  $S_a$ ,  $S_i$ , and  $S_r$  respectively (i.e.  $\operatorname{sort}(v_a[n]) = S_a[n]$  for all elements). P and Q return SMT formulae, which specify the instruction's behaviour thus:

- $P(v_a, v_i, v_r)$  is the *precondition*. If this formula does not hold, the instruction's behaviour is undefined. In the synthesis, we may ignore test cases where the precondition does not hold.

- $Q(v_a, v_i, v_r)$  is the *postcondition*. If  $P(v_a, v_i, v_r)$  holds,  $Q(v_a, v_i, v_r)$  also holds. Its purpose is to define  $v_r$  in terms of  $v_a$  and  $v_i$ .

$V(v_a, v_i, v_r)$  is a list of SMT expressions, namely the list of *valid pointers* for this instruction. Depending on whether the instruction is the synthesis' goal or a candidate, we either assume or require that the pointers in  $V(v_a, v_i, v_r)$  be valid.

Thus, as far as the synthesis algorithm is concerned, we can represent an instruction as a 6-tuple  $(S_a, S_i, S_r, P, Q, V)$ . To denote one of the elements of instruction *i*, we write  $S_a(i)$ , P(i) etc.

We now present some exemplary instruction definitions. In particular, we show how to model memory accesses.

### 3.1.1. Arithmetical instructions

Most arithmetical instructions are quite easy to define, because the bit-vector arithmetic defined in SMT-LIB is very similar to the usual arithmetic of a processor.

Thus, to represent an integral type of n bits, we choose an SMT bit vector of equal length (the sort  $BitVec_n$ ). We do not distinguish between signed and unsigned types, but define separate instruction for signed and unsigned arithmetic in the few cases where this is necessary.

Then, defining most arithmetical instructions is straightforward. For example, this is the definition of a 32-bit subtraction instruction:

$$\begin{split} S_a &= [\mathsf{BitVec}_{32},\mathsf{BitVec}_{32}]\\ S_i &= []\\ S_r &= [\mathsf{BitVec}_{32}]\\ P &= (v_a, v_i, v_r) \mapsto \mathsf{true}\\ Q &= (v_a, v_i, v_r) \mapsto v_r[0] = v_a[0] - v_a[1]\\ V &= (v_a, v_i, v_r) \mapsto []\\ \mathrm{sub32} &= (S_a, S_i, S_r, P, Q, V) \end{split}$$

However, bit shift operations are problematic, because there are different ways to deal with an out-of-range shift amount. In C, the shift amount must be nonnegative and less than the bit width, or the bit shift's behaviour is undefined. In the x86 assembly language and FIRM, the shift amount is interpreted as unsigned and implicitly reduced modulo the bit width.

We can specify both behaviours in our semantics. The interface is the same for both:

$$S_a = [\mathsf{BitVec}_{32}, \mathsf{BitVec}_{32}]$$

$$S_i = []$$

$$S_r = [\mathsf{BitVec}_{32}]$$

$$V = (v_a, v_i, v_r) \mapsto []$$

shr32 =  $(S_a, S_i, S_r, P, Q, V)$

Then, to use the C semantics, we define

$$P = (v_a, v_i, v_r) \mapsto 0 \le v_a[1] < 32$$

$$Q = (v_a, v_i, v_r) \mapsto v_r[0] = v_a[0] >> v_a[1]$$

and for the x86 and FIRM semantics, we define

$$P = (v_a, v_i, v_r) \mapsto \mathsf{true}$$

$$Q = (v_a, v_i, v_r) \mapsto v_r[0] = v_a[0] >> (v_a[1] \mod 32)$$

We can see that the compiler may translate a C shift operation as a FIRM shift operation (and, in turn, an x86 shift operation), because where the C operation is defined, the FIRM/x86 operation has the same behaviour. However, we lose the freedom to exploit the undefinedness of the C operation when we translate it to FIRM.

### 3.1.2. Memory Access

We model our memory access instructions like those in FIRM: They use and define values representing the current state of memory.

When SMT is used to describe program semantics, the memory state is usually represented as an SMT array (i.e. an associative map) [18]: An address space of 32 bits with 8 bit words being addressed is presented as an array from  $BitVec_{32}$  to  $BitVec_8$ . The SMT-LIB Array theory then provides the functions select and store, which directly implement the usual load and store operations.

However, this approach proved to be too inefficient for our needs. In the counterexample step of our algorithm (see Section 3.2.2), we found that the SMT solver could not prove with acceptable efficiency that no counterexample memory state exists. We therefore need to find a more efficient model for memory state.

As we can see from the overview algorithm (Algorithm 2 on Page 21), we only consider one machine instruction at a time as our goal. Therefore, we can restrict our memory model to only represent those addresses that the goal instruction uses (its valid pointer list). If a synthesis candidate uses any other addresses, we can exclude the candidate.

We have tried to specify this restriction in the Array theory, but the SMT solver could not make use of it. Therefore, we need to model the memory ourselves.

The memory state needs to hold two pieces of information for each valid pointer: Of course, it must store the value located at that address. In addition, it must store an *access flag* that is set when the address is loaded from.

We need the access flag for the following reason: A load operation does not change the state of our representation, but can actually have side-effects on volatile memory. Moreover, FIRM requires that a Load node produce a new M-value in order to encode write-after-read dependencies.

Therefore, we introduce an artificial change to the memory using the access flag. This way, the goal instruction and synthesis candidate are only deemed equivalent if they load from the same memory locations.

To generate an M-value sort M(g) for a goal instruction g with the valid pointer list V(g), we use a bit vector of size  $|V(g)| \cdot (w+1)$ , where w is the bit-width of the words being addressed.

This bit vector is laid out as follows: Bits  $k \cdot (w+1) + 1$  to  $k \cdot (w+1) + w$  hold the value located at the address V(g)[k]. The extra bit  $k \cdot (w+1)$  holds the access flag.

Defining load and store functions is then a matter of extracting and overwriting the right bits in the M-value. We also need not concern ourselves with handling invalid pointers, since the synthesis algorithm will ensure that all pointers are valid (see Section 3.2.2).

First, we define two primitives "ld" and "st" to load and store one word, and then build up the memory access instructions from these. For the following definitions, we use these abbreviations:

$$\begin{split} l(k) &:= k \cdot (w+1) + 1 & \text{Lower bound of } k\text{-th word} \\ u(k) &:= k \cdot (w+1) + w & \text{Upper bound of } k\text{-th word} \\ f(k) &:= k \cdot (w+1) & \text{Flag for } k\text{-th word} \\ n &:= |V(g)| \end{split}$$

The function "ld" is parameterised by V(g) (which we assume is externally defined), takes an M-value and an address to load from, and returns a new M-value and the value loaded:

$$\mathrm{ld}(m,a) = \begin{cases} (m[f(0) \mapsto 1], m[u(0) \dots l(0)]) & a = V(g)[0] \\ \vdots & \vdots \\ (m[f(k) \mapsto 1], m[u(k) \dots l(k)]) & a = V(g)[k] \\ \vdots & \vdots \\ (m[f(n-1) \mapsto 1], m[u(n-1) \dots l(n-1)]) & \text{otherwise} \end{cases}$$

Similarly, we define "st". It takes an M-value, an address and a value to store, and returns the updated M-value.

$$\operatorname{st}(m,a,v) = \begin{cases} m[n \cdot (w+1) \dots u(0) + 1] \circ v \circ m[l(0) - 1 \dots 0] & a = V(g)[0] \\ \vdots & \vdots \\ m[n \cdot (w+1) \dots u(k) + 1] \circ v \circ m[l(k) - 1 \dots 0] & a = V(g)[k] \\ \vdots & \vdots \\ m[n \cdot (w+1) \dots u(n-1) + 1] \circ v \circ m[l(n-1) - 1 \dots 0] & \text{otherwise} \end{cases}$$

In each definition's last case, we use the fact that we can assume the address to be valid. We therefore need not check against V(g)[n-1]. In the SMT solver's language, these definitions by cases become a chain of conditional assignments (called ite for if-then-else in SMT-LIB).

Having defined the load and store functions, we can now specify load and store instructions. For example, this is the specification of a 32-bit store instruction (again,

we assume that the goal instruction is globally defined):

$$\begin{split} S_a &= [M(g), \mathsf{BitVec}_{32}, \mathsf{BitVec}_{32}] \qquad (M\text{-}value, \ address, \ value) \\ S_i &= [] \\ S_r &= [M(g)] \\ P &= (v_a, v_i, v_r) \mapsto \mathsf{true} \\ Q &= (v_a, v_i, v_r) \mapsto \mathsf{let} \ m_0 = \mathsf{st}(v_a[0], v_a[1], v_a[2][7 \dots 0]) \ \mathsf{in} \\ \quad \mathsf{let} \ m_1 = \mathsf{st}(m_0, v_a[1] + 1, v_a[2][15 \dots 8]) \ \mathsf{in} \\ \quad \mathsf{let} \ m_2 = \mathsf{st}(m_1, v_a[1] + 2, v_a[2][23 \dots 16]) \ \mathsf{in} \\ \quad \mathsf{let} \ m_3 = \mathsf{st}(m_2, v_a[1] + 3, v_a[2][31 \dots 24]) \ \mathsf{in} \\ v_r[0] &= m_3 \\ V &= (v_a, v_i, v_r) \mapsto [v_a[1], v_a[1] + 1, v_a[1] + 2, v_a[1] + 3] \\ \mathsf{store32} &= (S_a, S_i, S_r, P, Q, V) \end{split}$$

#### Implementation Matters

For any instruction i, V(i) can easily be generated from Q(i): V(i) is the set of all values occurring as second arguments to ld or st. This also ensures that V(i) always stays consistent with Q(i).

However, the definitions of ld and st require the memory type M(g), and thus V(g), to be known (where g is the goal instruction). Thus, if Q(g) uses ld or st, we can only define it after V(g) is known, but we would like to extract V(g) from Q(g) automatically.

In order to break this cycle, the instructions do not define P, Q, and V directly, but specify their semantics in one function that takes a NodeEnv as its argument. NodeEnv is an abstract type with two implementations. The first implementation (the "dummy implementation") records all uses of ld and st to collect V. The second implementation uses V(g) to actually produce the SMT expressions for P and Qthat specify the instruction.

### 3.1.3. Constants

There are two kinds of constants we have to deal with, which differ in the point at which their value is defined.

Firstly, synthesis-time constants have their value chosen during synthesis. That value is the same for all instances of the instruction. For example, the IR equivalent of the increment instruction  $x_2 = inc(x_1)$  is  $x_2 = x_1 + 1$ , where 1 is a synthesis-time constant.

We represent synthesis-time constants with IR instructions that take no arguments and produce a constant from their internal attribute. They are equivalent to the Const node in FIRM in its different modes. For example, a 32-bit-wide constant is defined as follows:

$S_a = []$   $S_i = [\mathsf{BitVec}_{32}]$   $S_r = [\mathsf{BitVec}_{32}]$   $P = (v_a, v_i, v_r) \mapsto \mathsf{true}$   $Q = (v_a, v_i, v_r) \mapsto v_r[0] = v_i[0]$   $V = (v_a, v_i, v_r) \mapsto []$   $\mathsf{const32} = (S_a, S_i, S_r, P, Q, V)$

Secondly, there are *compile-time constants*. In assembly language, these occur as immediate arguments to instructions. Since it is very inefficient to generate separate rules for every possible immediate, the synthesis actually treats compile-time constants as arguments of the instruction that are marked as constant.

The synthesis then proceeds as normal, and it is up to the code generator to emit the tests required to ensure that the argument in question is in fact a compile-time constant.

### 3.1.4. Conditional Control Flow

Many IRs handle conditional control flow similarly, but still differ slightly (compare LLVM's icmp and br [19] to FIRM's Cmp and Cond). Therefore, the following section is FIRM-specific, but can be adapted to other IRs.

To represent control flow, we need to represent three additional modes:

- To represent boolean values, we use the built-in sort Bool

- To represent the possible relations for a comparison, we use a 3-bit bit vector. Bit 2 represents the relation "greater than", bit 1 represents "less than", and bit 0 represents "equal to". Relations are combined by settings multiple bits. For example, relation number 6 is "greater than or less than", i.e. "not equal to". The three bits correspond to the three bits in FIRM's type ir\_relation [4] that are used for integers (ir\_relation\_unordered is only used for floating-point comparisons).

- To represent control flow, we also use the sort **Bool**, whereby **true** represents a branch being taken.

With these new modes, we can represent the Cmp node, using an internal attribute for the relation. See the FIRM API documentation for all possible relation values.

Signedness matters in the comparison instruction. FIRM determines whether to use signed or unsigned comparison based on the arguments' modes; we define two variants of the instruction. Both definitions look exactly the same, only the meaning of the relational operators is changed.

$$\begin{split} S_{a} &= [\mathsf{BitVec}_{32},\mathsf{BitVec}_{32}] \\ S_{i} &= [\mathsf{BitVec}_{3}] \\ S_{r} &= [\mathsf{Bool}] \\ P &= (v_{a},v_{i},v_{r}) \mapsto \mathsf{true} \\ Q &= (v_{a},v_{i},v_{r}) \mapsto v_{r}[0] = \begin{cases} \mathsf{false} & v_{i}[0] = 0 \\ v_{a}[0] = v_{a}[1] & v_{i}[0] = 1 \\ \vdots & \vdots \\ v_{a}[0] \neq v_{a}[1] & v_{i}[0] = 1 \\ \vdots & \vdots \\ v_{a}[0] \neq v_{a}[1] & v_{i}[0] = 6 \\ \mathsf{true} & v_{i}[0] = 7 \end{cases} \\ V &= (v_{a},v_{i},v_{r}) \mapsto [] \\ \mathsf{cmp32} &= (S_{a},S_{i},S_{r},P,Q,V) \end{split}$$

When defining any control flow node, we must be careful to set exactly one of the control flow results to **true**, and the rest to **false**. Other than that, the definition of the Cond node is simple. It produces two control flow results. The first result is the branch taken if the input is false, the second result is taken if the input is true.

$$\begin{split} S_a &= [\mathsf{Bool}]\\ S_i &= []\\ S_r &= [\mathsf{Bool}, \mathsf{Bool}]\\ P &= (v_a, v_i, v_r) \mapsto \mathsf{true}\\ Q &= (v_a, v_i, v_r) \mapsto v_r[0] = \neg v_a[0] \land v_r[1] = v_a[0]\\ V &= (v_a, v_i, v_r) \mapsto []\\ \mathrm{cond} &= (S_a, S_i, S_r, P, Q, V) \end{split}$$

### 3.1.5. Machine Instructions

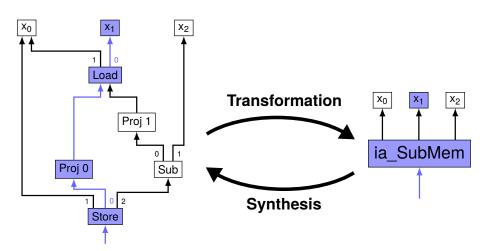

We define machine instructions in the same way, but these may be more complex for CISC machines. For example, the following is the definition of a 32-bit-wide subtraction of a value from a location in memory (such as the x86 instruction sub %eax, x, where x is a global variable).

In comparison with the IR instruction store32, the order of M-value and address is reversed in the argument sequence. This is because we follow the interface set by the nodes in the FIRM x86 back end.

$$\begin{split} S_a &= [\mathsf{BitVec}_{32}, M(g), \mathsf{BitVec}_{32}] \qquad (address, \ M-value, \ subtrahend) \\ S_i &= [] \\ S_r &= [M(g)] \\ P &= (v_a, v_i, v_r) \mapsto \mathsf{true} \\ Q &= (v_a, v_i, v_r) \mapsto \mathsf{let} \ (m_0, x_0) = \mathsf{ld}(v_a[1], v_a[0]) \ \mathsf{in} \\ &= \mathsf{let} \ (m_1, x_1) = \mathsf{ld}(m_0, v_a[0] + 1) \ \mathsf{in} \\ &= \mathsf{let} \ (m_2, x_2) = \mathsf{ld}(m_1, v_a[0] + 2) \ \mathsf{in} \\ &= \mathsf{let} \ (m_3, x_3) = \mathsf{ld}(m_2, v_a[0] + 3) \ \mathsf{in} \\ &= \mathsf{let} \ (m_3, x_3) = \mathsf{ld}(m_2, v_a[0] + 3) \ \mathsf{in} \\ &= \mathsf{let} \ x' = x - v_a[2] \ \mathsf{in} \\ &= \mathsf{let} \ m_4 = \mathsf{st}(m_3, v_a[0], x'[7 \dots 0]) \ \mathsf{in} \\ &= \mathsf{let} \ m_5 = \mathsf{st}(m_4, v_a[0] + 1, x'[15 \dots 8]) \ \mathsf{in} \\ &= \mathsf{let} \ m_7 = \mathsf{st}(m_6, v_a[0] + 3, x'[31 \dots 24]) \ \mathsf{in} \\ &= v_r[0] = m_7 \\ V = (v_a, v_i, v_r) \mapsto [v_a[0], v_a[0] + 1, v_a[0] + 2, v_a[0] + 3] \\ \mathsf{ia-submem} 32 = (S_a, S_i, S_r, P, Q, V) \end{split}$$

### **Control Flow In Machine Instructions**

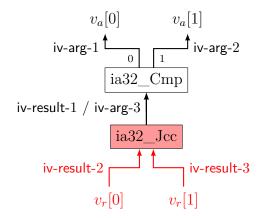

Where control flow is concerned, machine architectures differ significantly. Our target architecture is x86, which has a generic comparison instruction, and encodes the relation to check for in the conditional jump. Other machines, such as MIPS, use an approach more like FIRM's.

The x86 compare instruction ia-cmp32 sets the processor's *flags* [20], and the conditional jump instructions evaluate them [21]. We represent the arithmetic flags OF, SF, ZF, PF, and CF in a 5-bit bit vector.

The computation of SF, ZF, PF, and CF is straightforward. To compute OF, consider the following ( $\oplus$  represents exclusive or): Let s(x) be the sign bit of x, and let ci be the bit carried into the sign bit during the computation a - b. Then OF is defined as  $ci \oplus CF$ , since CF is the carry out of the sign bit. On the other hand, we have  $s(a - b) = s(a) \oplus s(b) \oplus ci$ , because - and  $\oplus$  are the same function on single bits. From this follows OF  $= s(a - b) \oplus s(a) \oplus s(b) \oplus CF$ .

As with the IR comparison instruction, the relation to check (the *condition code*) is an internal attribute, but in this case one of the jump instruction. There are 16 possible condition codes for integers, which we represent in the same way as the type x86\_condition\_code\_t in FIRM's x86 back end.

We define ia-cmp32 and ia-jcc as follows, whereby the if-then-else function ite returns the second argument, if the first argument is true, and the third one otherwise.

$$\begin{split} S_a &= [\mathsf{Bit}\mathsf{Vec}_{32},\mathsf{Bit}\mathsf{Vec}_{32}]\\ S_i &= []\\ S_r &= [\mathsf{Bit}\mathsf{Vec}_5]\\ P &= (v_a, v_i, v_r) \mapsto \mathsf{true}\\ Q &= (v_a, v_i, v_r) \mapsto \mathsf{let} \ s &= v_a[0] - v_a[1] \ \mathsf{in}\\ &\quad \mathsf{let} \ SF &= s[31 \dots 31] \ \mathsf{in}\\ &\quad \mathsf{let} \ SF &= s[31 \dots 31] \ \mathsf{in}\\ &\quad \mathsf{let} \ ZF &= \mathsf{ite}(s = 0, 1, 0) \ \mathsf{in}\\ &\quad \mathsf{let} \ PF &= \bigoplus_{i=0}^7 s[i \dots i] \ \mathsf{in}\\ &\quad \mathsf{let} \ CF &= \mathsf{ite}(v_a[0] <_{unsigned} v_a[1], 1, 0) \ \mathsf{in}\\ &\quad \mathsf{let} \ OF &= SF \oplus v_a[0][31 \dots 31] \oplus v_a[1][31 \dots 31] \oplus CF \ \mathsf{in}\\ v_r[0] &= OF \circ SF \circ ZF \circ PF \circ CF\\ V &= (v_a, v_i, v_r) \mapsto []\\ \mathsf{ia-cmp32} &= (S_a, S_i, S_r, P, Q, V) \end{split}$$

$$\begin{split} S_{a} &= [\mathsf{Bit}\mathsf{Vec}_{5}] \\ S_{i} &= [\mathsf{Bit}\mathsf{Vec}_{4}] \\ S_{r} &= [\mathsf{Bool},\mathsf{Bool}] \\ P &= (v_{a}, v_{i}, v_{r}) \mapsto \mathsf{true} \\ Q &= (v_{a}, v_{i}, v_{r}) \mapsto \mathsf{let} \ OF &= v_{a}[0][4] \ \mathsf{in} \\ &\quad \mathsf{let} \ SF &= v_{a}[0][3] \ \mathsf{in} \\ &\quad \mathsf{let} \ SF &= v_{a}[0][2] \ \mathsf{in} \\ &\quad \mathsf{let} \ PF &= v_{a}[0][1] \ \mathsf{in} \\ &\quad \mathsf{let} \ CF &= v_{a}[0][0] \ \mathsf{in} \\ \\ &\quad \mathsf{let} \ CF &= v_{a}[0][0] \ \mathsf{in} \\ &\quad \mathsf{let} \ CF &= v_{a}[0][0] \ \mathsf{in} \\ &\quad \mathsf{let} \ SF &= 0 \\ OF &= 0 \\ &\quad \mathsf{v}_{i}[0] &= 1 \\ &\quad \mathsf{in} \\ \\ &\quad \mathsf{ZF} &= 0 \land SF &= OF \\ v_{i}[0] &= 15 \\ v_{r}[0] &= \neg j \land v_{r}[1] &= j \\ V &= (v_{a}, v_{i}, v_{r}) \mapsto [] \\ &\quad \mathsf{ia-jcc} &= (S_{a}, S_{i}, S_{r}, P, Q, V) \end{split}$$

The difference between the way that the IR and the machine language handle control flow leads to a problem for the synthesis: From the overview algorithm

# **Figure 3.1.:** A graph pattern consisting of a comparison and conditional jump instruction. We use this pattern as an example to construct a compound instruction.

(Algorithm 2 on Page 21), we can see that the synthesis searches for an IR pattern that implements a single instruction. However, the FIRM IR does not use flags, so no IR pattern can represent a machine instruction that uses or produces a flag value. To solve this problem, we introduce *compound instructions*.

### 3.1.6. Compound Instructions

A compound instruction is an instruction defined through a graph pattern. For example, the graph pattern shown in Figure 3.1 can define a compound instruction to represent the instructions cmp x, y; jl label as a unit.

To build an SMT formula for the precondition or postcondition of a compound instruction c (i.e. P(c) or Q(c)), we first introduce fresh intermediate variables for every instruction in c's graph pattern. Then, we construct P(i) or Q(i) for every instruction i in the pattern. Finally, for each edge in the pattern, we assert that the values it connects should be equal.

Taking the compound instruction defined by the pattern in Figure 3.1 as an example, we get the following for Q(c) (the condition code for "less than" is 12):